# D9050PCIC PCI Express® Compliance Test Application

# **Notices**

#### © Keysight Technologies 2023

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### **Trademarks**

PCI-SIG<sup>®</sup>, PCIe<sup>®</sup>, and the PCI Express<sup>®</sup> are US registered trademarks and/or service marks of PCI-SIG.

#### Version

Version 5.1.0.0

#### Edition

Twelfth Edition, September 2023

Available in electronic format only

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

# Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES. EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

# **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

# U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

# Safety Notices

# **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# PCI Express Automated Testing—At A Glance

The Keysight D9050PCIC PCI Express<sup>®</sup> Automated Test Application helps you verify PCI Express device under test (DUT) compliance to specifications using Keysight Z-Series or UXR Series Infiniium oscilloscope. The PCI Express<sup>®</sup> Automated Test Application:

- · Lets you select individual or multiple tests to run.

- · Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- · Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run and lets you specify the thresholds at which marginal or critical warnings appear.

- · Creates a printable HTML report of the tests that have been run.

NOTE

The tests performed by the PCI Express<sup>®</sup> Automated Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

NOTE

D9050PCIC PCI Express Compliance Test Application supports two channel scope. In case of two channel scope, only channel 1 and 2 will be available.

NOTE

D9050PCIC PCI Express Compliance Test Application supports D9010AGGC Compliance Test Software Measurement Server for using multiple machines/PCs over a network as acquisition engines and processing engines in order to significantly enhance the test execution speed. To know more, please see the D9010AGGC product page on keysight.com.

NOTE

This document covers the methods of implementation for PCIe 5.0 and PCIe 6.0 devices. For PCIe 4.0 devices, please see the Keysight D9040PCIC PCI Express Compliance Test Application Methods of Implementation document.

# Required Equipment and Software

In order to run the PCI Express automated tests, you need the following equipment and software:

- D9050PCIC PCI Express<sup>®</sup> Automated Test Application software and license

- MATLAB Run Time R2021a (9.10)

- Intel Clock Jitter Tool 5.0.2

- (https://www.intel.com/content/www/us/en/content-details/652180/clock-jitter-tool-5-0-2.html)

- Use one of the following oscilloscope models:

- Keysight Z-Series Infiniium Oscilloscope

- Keysight UXR Series Infiniium Oscilloscope

- · E2688A Serial Data Analysis and Clock Recovery software

- Keyboard, qty = 1, (provided with the Keysight Infiniium Series Oscilloscope)

- Mouse, qty = 1, (provided with the Keysight Infiniium Series Oscilloscope)

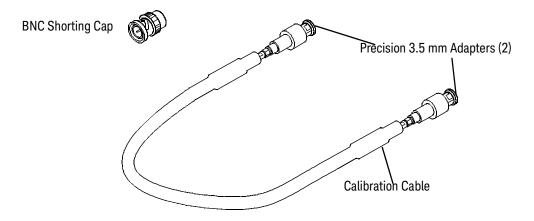

- Precision 3.5 mm BNC to SMA male adapter, qty = 2 (provided with the Keysight Infiniium Series Oscilloscope)

- 50-ohm Coax Cable with SMA Male Connectors 24-inch or less RG-316/U or similar, qty = 2, matched length

## In This Book

This manual describes the tests that are performed by the PCI Express<sup>®</sup> Automated Test Application in more detail; it contains information from (and refers to) the base specification, and it describes how the tests are performed.

This manual is divided into following sections:

- "Introduction" covers the software and license installation and test preparation guide.

- "PCI-Express Gen5 2.5 GT/s Tests" covers the PCI Express Gen 5 tests and methods of implementation at 2.5 GT/s.

- "PCI Express Gen 5 5.0 GT/s Tests" covers the PCI Express Gen 5 tests and methods of implementation at 5.0 GT/s.

- "PCI-Express Gen 5 8.0 GT/s Tests" covers the PCI Express Gen 5 tests and methods of implementation at 8.0 GT/s.

- · "PCI Express Gen 5 16.0 GT/s Tests" covers the PCI Express Gen 5 tests and methods of implementation at 16.0 GT/s.

- "PCI Express Gen5 32.0 GT/s Tests" covers the PCI Express Gen 5 tests and methods of implementation at 32.0 GT/s.

- "PCI-Express Gen6 2.5 GT/s Tests" covers the PCI Express Gen 6 tests and methods of implementation at 2.5 GT/s.

- · "PCI Express Gen6 5.0 GT/s Tests" covers the PCI Express Gen 6 tests and methods of implementation at 5.0 GT/s.

- "PCI-Express Gen6 8.0 GT/s Tests" covers the PCI Express Gen 6 tests and methods of implementation at 8.0 GT/s.

- · "PCI Express Gen6 16.0 GT/s Tests" covers the PCI Express Gen 6 tests and methods of implementation at 16.0 GT/s.

- · "PCI Express Gen6 32.0 GT/s Tests" covers the PCI Express Gen 6 tests and methods of implementation at 32.0 GT/s.

- · "PCI Express Gen6 64.0 GT/s Tests" covers the PCI Express Gen 6 tests and methods of implementation at 64.0 GT/s.

- · "Appendices" covers oscilloscope calibration, channel de-skew calibration, and index information.

#### The chapters in this book are:

- Chapter 1, "Installing the PCI Express Compliance Test Application" shows how to install and license the automated test application software (if it was purchased separately).

- Chapter 2, "Preparing to Take Measurements" shows how to start the PCI Express® Automated Test Application and gives a brief overview of how it is used.

- Chapter 3, "Reference Clock Tests, PCI-E 5.0" contains more information on the PCI Express version 5.0 reference clock tests for all data rates.

- Chapter 4, "Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 transmitter tests at 2.5 GT/s data rate.

- Chapter 5, "CEM-EndPoint Tests, 2.5 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0

CEM-endpoint tests at 2.5 GT/s data rate.

- Chapter 6, "CEM-RootComplex Tests, 2.5 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0

CEM-rootcomplex tests at 2.5 GT/s data rate.

- Chapter 7, "Reference Clock Tests, 2.5 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 reference clock tests at 2.5 GT/s data rate.

- Chapter 8, "Transmitter (Tx) Tests, 5.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 transmitter tests at 5.0 GT/s data rate.

- Chapter 9, "CEM-EndPoint Tests, 5.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM-endpoint tests at 5.0 GT/s data rate.

- Chapter 10, "CEM-RootComplex Tests, 5.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM rootcomplex tests at 5.0 GT/s data rate.

- Chapter 11, "Reference Clock Tests, 5.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 reference clock tests at 5.0 GT/s data rate.

- Chapter 12, "Transmitter (Tx) Tests, 8.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 transmitter tests at 8.0 GT/s data rate.

- Chapter 13, "CEM-EndPoint Tests, 8.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM-endpoint tests at 8.0 GT/s data rate.

- Chapter 14, "CEM-RootComplex Tests, 8.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM-rootcomplex tests at 8.0 GT/s data rate.

- Chapter 15, "Reference Clock Tests, 8.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 reference clock tests at 8.0 GT/s data rate.

- Chapter 16, "Transmitter (Tx) Tests, 16.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 transmitter tests at 16.0 GT/s data rate.

- Chapter 17, "CEM-EndPoint Tests, 16.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0

CEM-endpoint tests at 16.0 GT/s data rate.

- Chapter 18, "CEM-RootComplex Tests, 16.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM-rootcomplex tests at 16.0 GT/s data rate.

- Chapter 19, "Reference Clock Tests, 16.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 reference clock tests at 16.0 GT/s data rate.

- Chapter 20, "Transmitter (Tx) Tests, 32.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 transmitter tests at 32.0 GT/s data rate.

- Chapter 21, "CEM-EndPoint Tests, 32.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM-endpoint tests at 32.0 GT/s data rate.

- Chapter 22, "CEM-RootComplex Tests, 32.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 CEM-rootcomplex tests at 32.0 GT/s data rate.

- Chapter 23, "Reference Clock Tests, 32.0 GT/s, PCI-E 5.0" contains more information on the PCI Express version 5.0 reference clock tests at 32.0 GT/s data rate.

- Chapter 24, "Reference Clock Tests, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at all data rates.

- Chapter 25, "Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 transmitter tests at 2.5 GT/s data rate.

- Chapter 26, "Reference Clock Tests, 2.5 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at 2.5 GT/s data rate.

- Chapter 27, "Transmitter (Tx) Tests, 5.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 transmitter tests at 5.0 GT/s data rate.

- Chapter 28, "Reference Clock Tests, 5.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at 5.0 GT/s data rate.

- Chapter 29, "Transmitter (Tx) Tests, 8.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 transmitter tests at 8.0 GT/s data rate.

- Chapter 30, "Reference Clock Tests, 8.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at 8.0 GT/s data rate.

- Chapter 31, "Transmitter (Tx) Tests, 16.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 transmitter tests at 16.0 GT/s data rate.

- Chapter 32, "Reference Clock Tests, 16.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at 16.0 GT/s data rate.

- Chapter 33, "Transmitter (Tx) Tests, 32.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 transmitter tests at 32.0 GT/s data rate.

- Chapter 34, "Reference Clock Tests, 32.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at 32.0 GT/s data rate.

- Chapter 35, "Transmitter (Tx) Tests, 64.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 transmitter tests at 64.0 GT/s data rate.

- Chapter 36, "Reference Clock Tests, 64.0 GT/s, PCI-E 6.0" contains more information on the PCI Express version 6.0 reference clock tests at 64.0 GT/s data rate.

- Appendix A, "Calibrating the Digital Storage Oscilloscope" describes how to calibrate the oscilloscope in preparation for running the PCI Express automated tests.

- Appendix B, "INF\_SMA\_Deskew.set Setup File Details" describes a setup used when performing channel de-skew calibration.

6

# See Also,

The PCI Express® Automated Test Application's online help, which describes:

- PCI Express Automated Testing-At a Glance

- Creating or Opening a Test Project

- Setting Up the Test Environment

- Test Mode

- Device Definition

- Connection Setup

- Test Report User Comments

- Selecting Tests

- Configuring Tests

- Verifying Physical Connections

- Running Tests

- Options to Start Test Runs

- Settings to Optimize Test Runs

- Configuring Automation in the Test Application

- Using Script for Automation

- Using Files for Automation

- Running Automation Script or Files

- Viewing Results

- Viewing HTML Test Report

- Exiting the Test Application

- Additional Settings in the Test App

- Customizing the Test Application

- · File Menu Options

- View Menu Options

- Tools Menu Options

- Help Menu Options

- Controlling the Application via a Remote PC

- Using a Second Monitor

# Contents

PCI Express Automated Testing—At A Glance 3

Required Equipment and Software 4

In This Book 4

See Also, 7

# Part I

Introduction 29

1 Installing the PCI Express Compliance Test Application

**Installing the Software** 32

Installing the License Key 33

Using Keysight License Manager 5 33 Using Keysight License Manager 6 34

2 Preparing to Take Measurements

Calibrating the Oscilloscope 38

**Starting the PCI Express Compliance Test Application** 39

Online Help Topics 41

# Part II

PCI-Express Gen5 All GT/s Tests 43

3 Reference Clock Tests, PCI-E 5.0

Reference Clock Measurement Point 46

# Running Reference Clock Tests 47

Rising Edge Rate Test 48

Falling Edge Rate Test 50

Average Clock Period Test 52

Duty Cycle Test 54

Differential Input High Voltage Test 56

Differential Input Low Voltage Test 58

Absolute Crossing Point Voltage Test 60

Variation of V<sub>Cross</sub> Test 62

Clock Frequency (Common Clk) 64

Absolute Max Input Voltage Test 65

Absolute Min Input Voltage Test 67

Rise-Fall Matching Test 69

RefClk SSC Frequency Range (Common Clk) Test 72

RefClk SSC Deviation (Common Clk) Test 73

RefClk Max SSC df/dt (Slew Rate) (Common Clk) Test 74

#### Part III

# PCI-Express Gen5 2.5 GT/s Tests 77

# 4 Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 5.0

# Tx Compliance Test Load 80

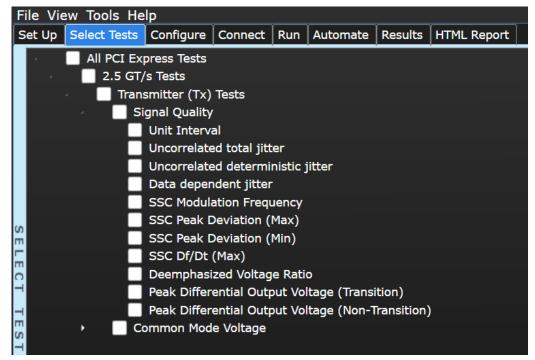

# Running Tx Tests 81

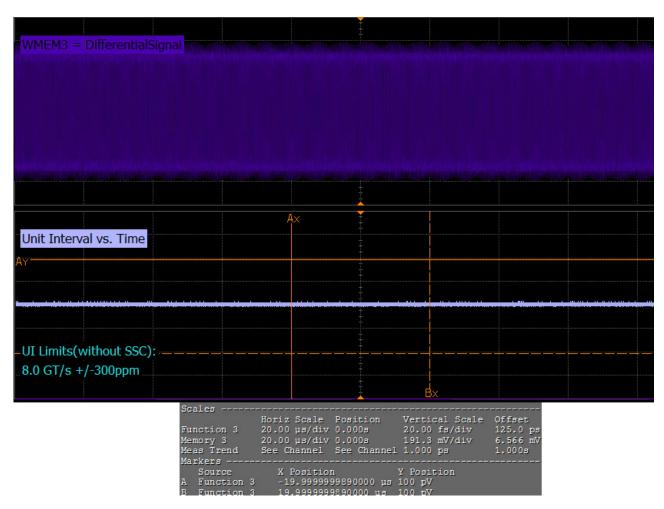

Unit Interval Test 82

Uncorrelated Total Jitter Test 85

Uncorrelated Deterministic Jitter Test 86

Data Dependent Jitter (Information-Only Test) 87

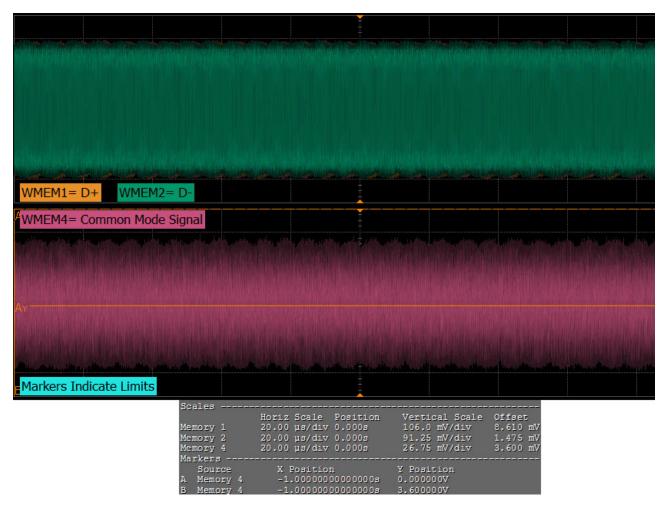

DC Common-Mode Voltage Test 88

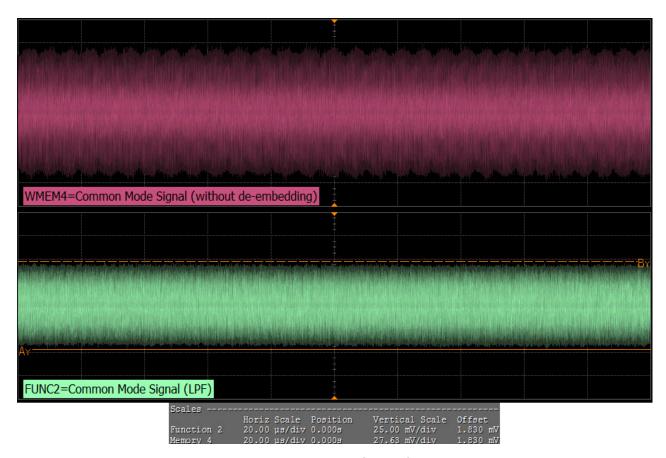

AC Common-Mode Voltage (LPF, 1.25 GHz) Test 90

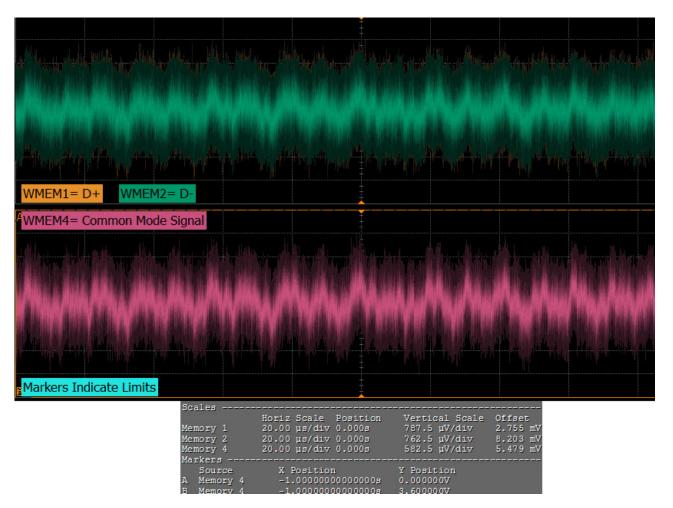

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 92

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 94

SSC Modulation Frequency 96

SSC Peak Deviation (Max) 97

SSC Peak Deviation (Min) 98

SSC Max df/dt (Slew Rate) Test 99

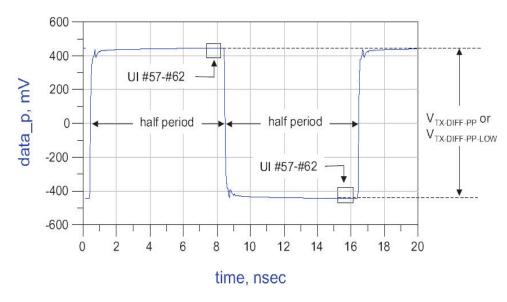

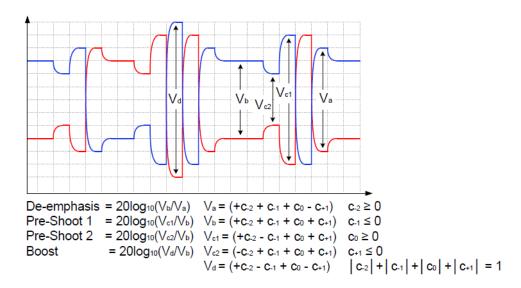

Deemphasized Voltage Ratio Test 101

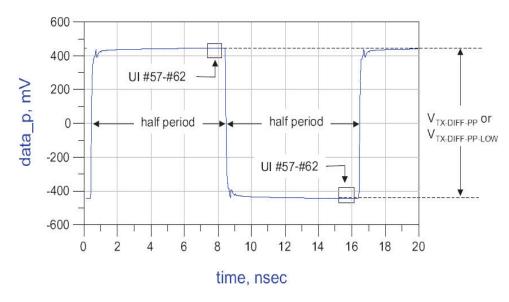

Peak Differential Output Voltage (Transition) Test 105

Peak Differential Output Voltage (Non-Transition) Test 109

# 5 CEM-EndPoint Tests, 2.5 GT/s, PCI-E 5.0

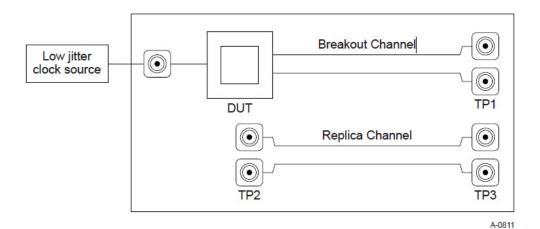

# Probing the Link for CEM-EndPoint Compliance 114

Connecting the Compliance Base Board for CEM-EndPoint Testing 114

# **Running CEM-EndPoint Tests** 115

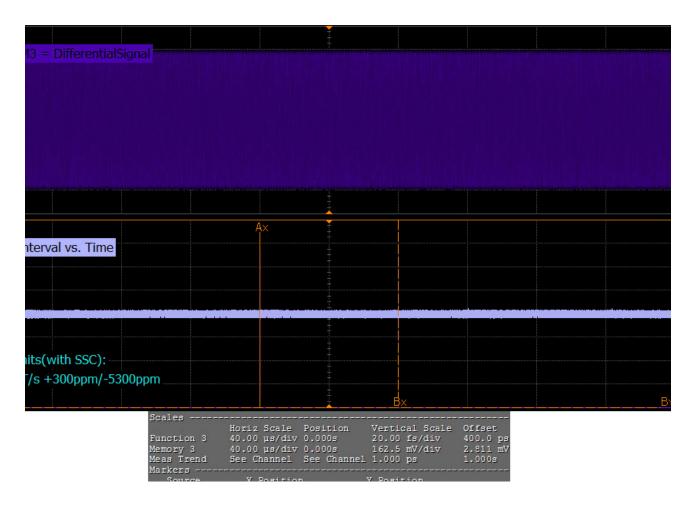

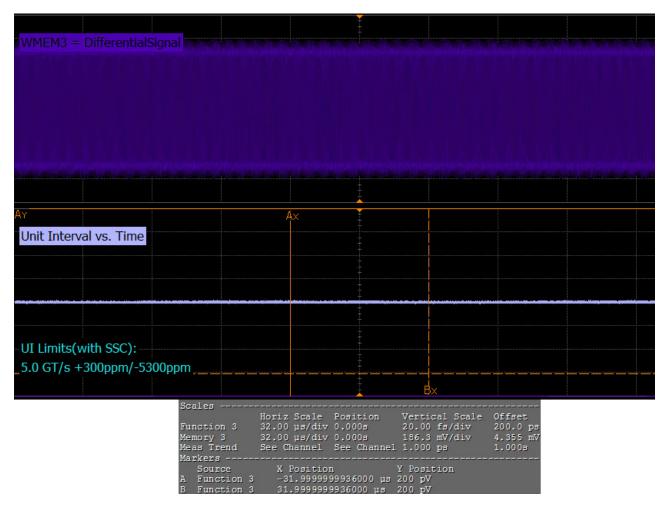

Unit Interval Test (Information Only) 116

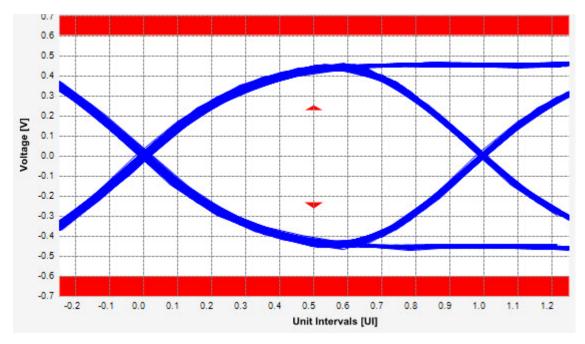

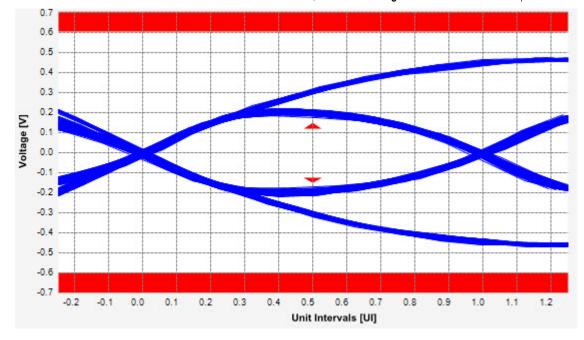

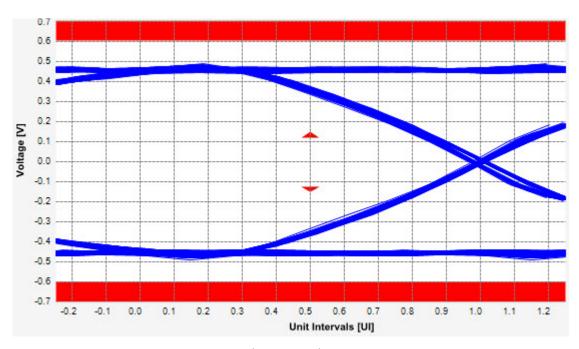

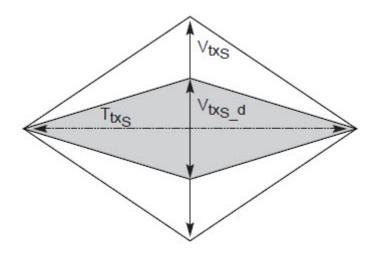

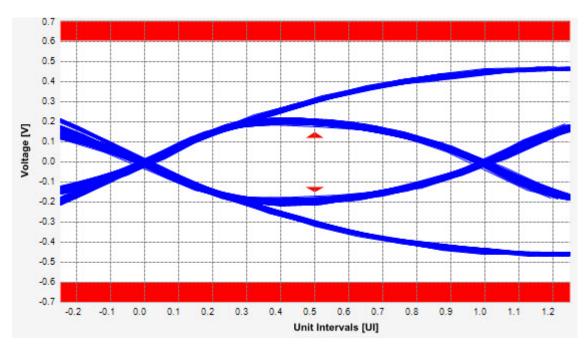

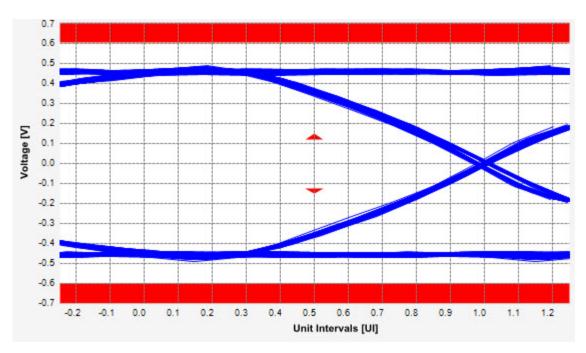

Template Test 118

Median to Max Jitter Test 121

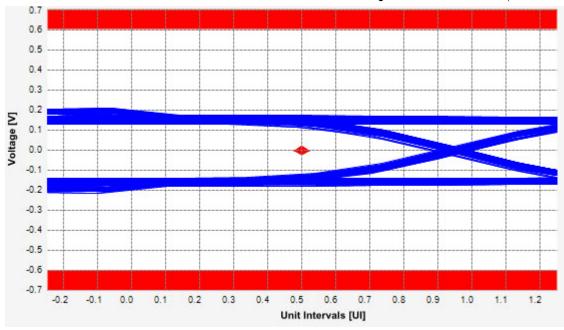

Eye-Width Test 123

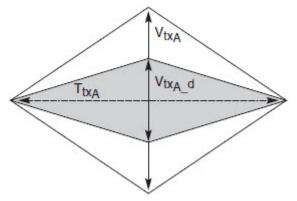

Peak Differential Output Voltage Test (Transition) 125

Peak Differential Output Voltage Test (Non-Transition) 127

# 6 CEM-RootComplex Tests, 2.5 GT/s, PCI-E 5.0

# Probing the Link for CEM-RootComplex Compliance 132

Connecting the Signal Quality Load Board for System/Motherboard Testing 132

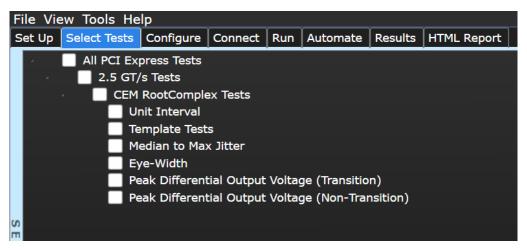

# Running CEM-RootComplex Tests 133

Unit Interval Test 134

Template Tests 136

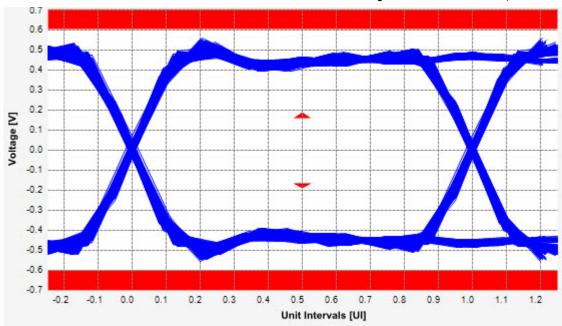

Median to Max Jitter Test 139

Eye-Width Test 141

Peak Differential Output Voltage (Transition) Test 14

Peak Differential Output Voltage (Non-Transition) Test 145

# 7 Reference Clock Tests, 2.5 GT/s, PCI-E 5.0

# Reference Clock Architectures 150

Common Clock Architecture 150

Reference Clock Measurement Point 152

# Running Reference Clock Tests 153

Peak to Peak Jitter (Common Clk) Test 154

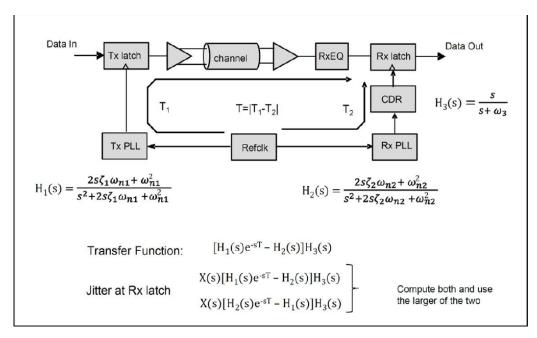

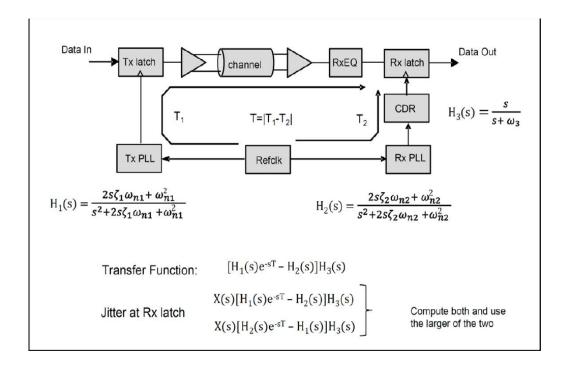

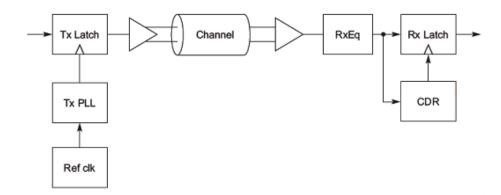

PCI-SIG Reference Clock Jitter 159

## Part IV

# PCI-Express Gen5 5.0 GT/s Tests 161

# 8 Transmitter (Tx) Tests, 5.0 GT/s, PCI-E 5.0

# **Tx Compliance Test Load** 164

# **Running Tx Tests** 165

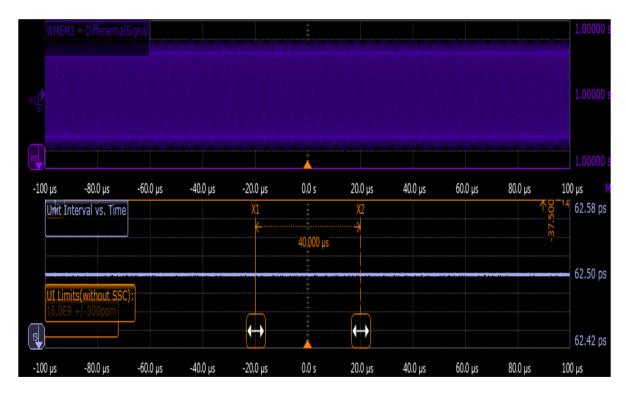

Unit Interval Test 166

Uncorrelated Total Jitter Test 168

Uncorrelated Deterministic Jitter Test 169

Total Uncorrelated PWJ (Pulse Width Jitter) Test 170

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 171

Data Dependent Jitter (Information-Only Test) 172

Random Jitter Test (Information Only Test) 173

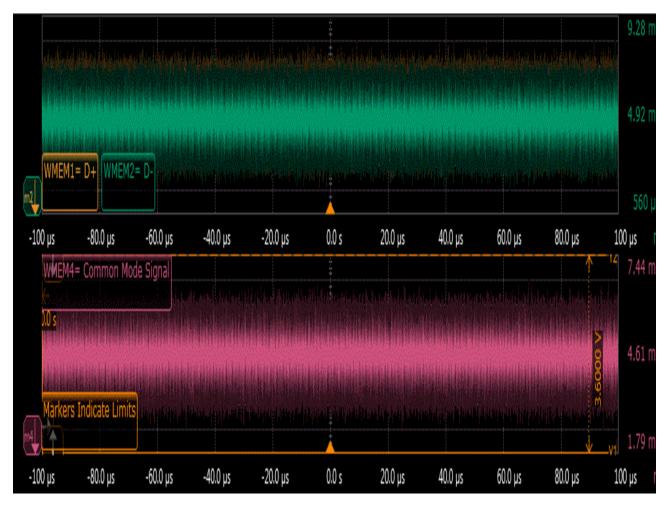

DC Common-Mode Voltage Test 174

AC Common-Mode Voltage (LPF, 2.5 GHz) Test 176

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 177

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 179

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 181

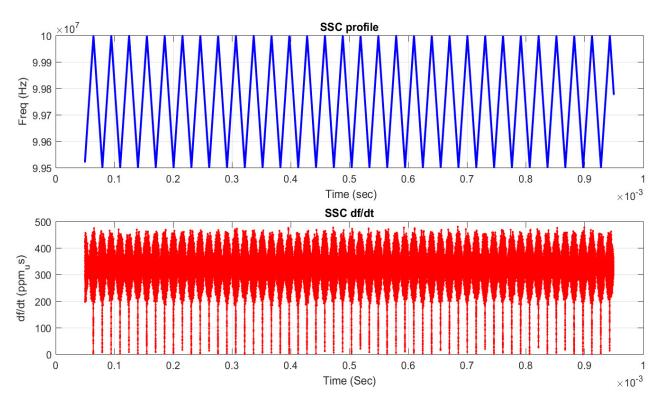

SSC Modulation Frequency 183

SSC Peak Deviation (Max) 184

SSC Peak Deviation (Min) 185

SSC Max df/dt (Slew Rate) Test 186

Deemphasized Voltage Ratio Test 188

Peak Differential Output Voltage (Transition) Test 192

Peak Differential Output Voltage (Non-Transition) Test 196

# 9 CEM-EndPoint Tests, 5.0 GT/s, PCI-E 5.0

# **Probing the Link for CEM-EndPoint Compliance** 202

Connecting the Compliance Base Board for CEM-EndPoint Testing 202

# Running CEM-EndPoint Tests 203

Unit Interval Test 204

Template Tests 206

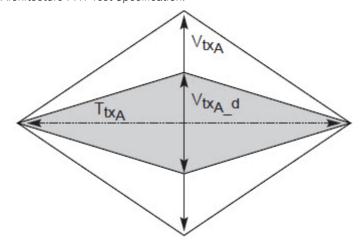

Peak Differential Output Voltage (Transition) Test 210

Peak Differential Output Voltage (Non-Transition) Test 213

Eye-Width Test 216

RMS Random Jitter Test (Information Only) 218

Maximum Deterministic Jitter Test 220

Total Jitter at BER-12 Test 222

# 10 CEM-RootComplex Tests, 5.0 GT/s, PCI-E 5.0

## Probing the Link for CEM-RootComplex Compliance 226

Connecting the Signal Quality Load Board for System/Motherboard Testing 226

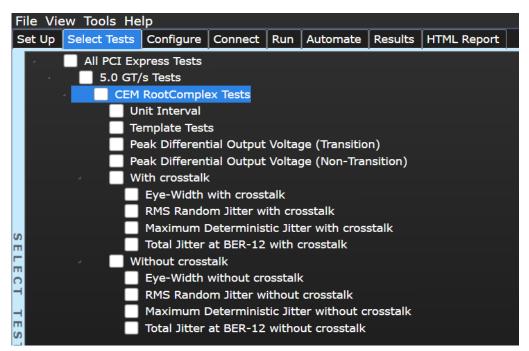

# Running CEM-RootComplex Tests 227

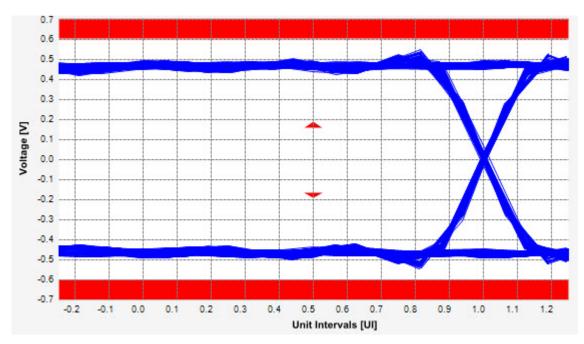

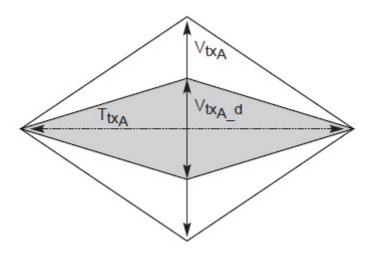

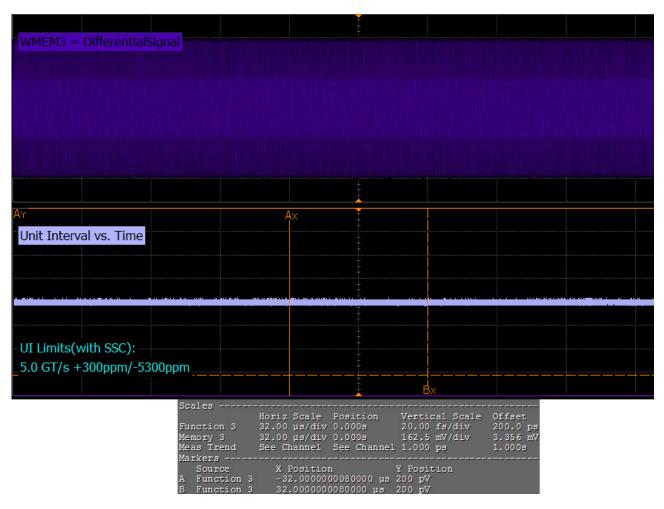

Unit Interval Test (Information only) 228

Template Tests 231

Peak Differential Output Voltage (Transition) Test 235

Peak Differential Output Voltage (Non-Transition) Test 237

Eye-Width Test 240

RMS Random Jitter Test (Information Only) 243

Maximum Deterministic Jitter Test 245

Total Jitter at BER-12 Test 247

# 11 Reference Clock Tests, 5.0 GT/s, PCI-E 5.0

# Reference Clock Architectures 250

Common Clock Architecture 250

Reference Clock Measurement Point 252

# Running Reference Clock Tests 253

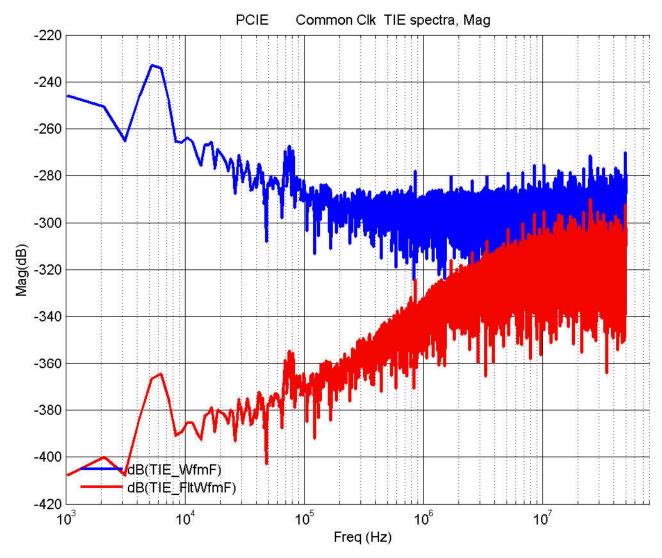

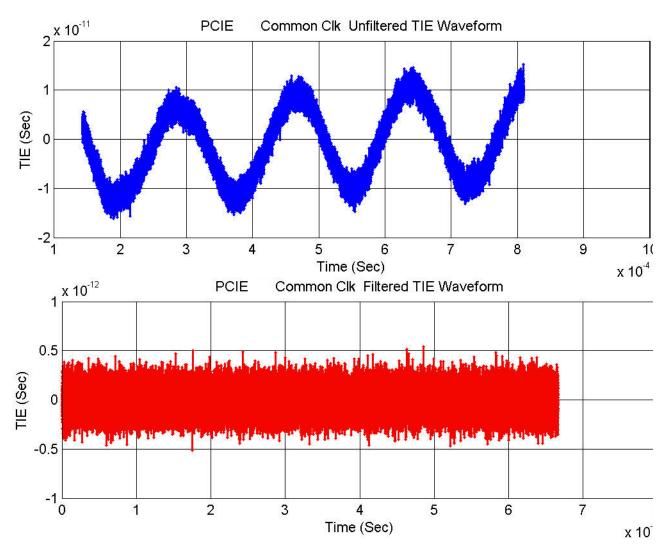

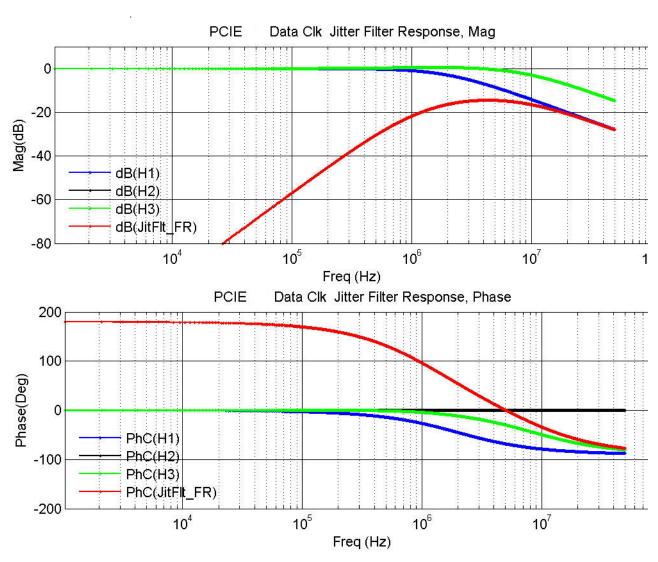

RMS Jitter (Common Clk) Test 254 PCI-SIG Reference Clock Jitter 259

261

# Part V PCI-Express Gen5 8.0 GT/s Tests

# 12 Transmitter (Tx) Tests, 8.0 GT/s, PCI-E 5.0

# **Tx Compliance Test Load** 264

# Running Tx Tests 265

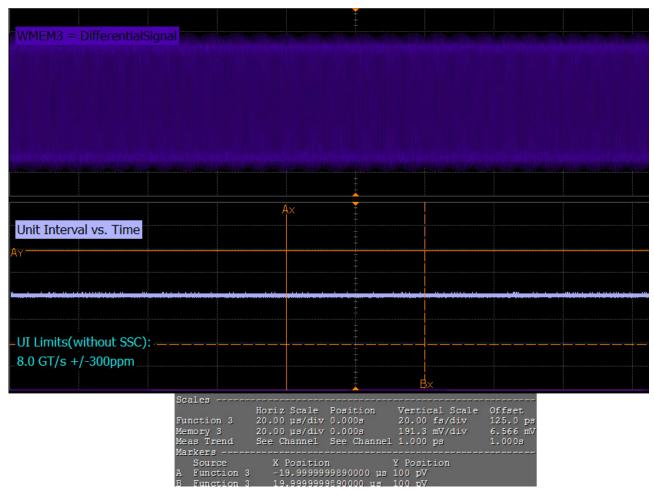

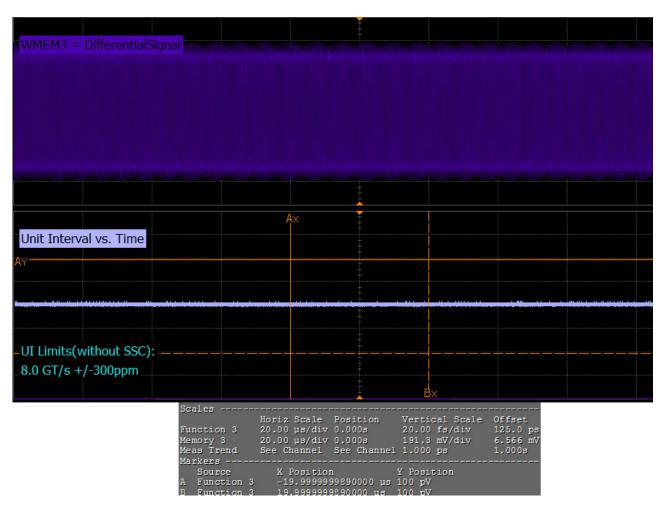

Unit Interval Test 266

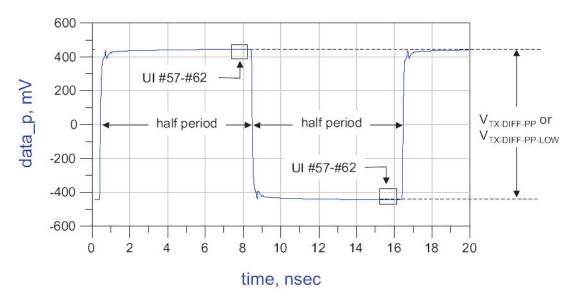

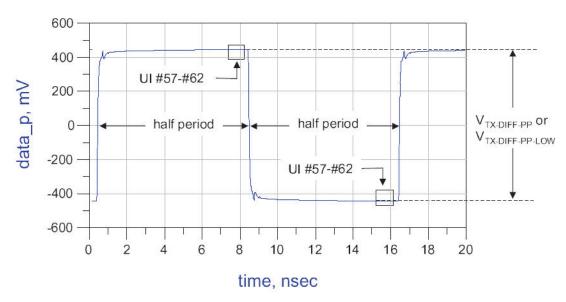

Full Swing Tx Voltage with no TxEQ Test 269

Reduced Swing Tx Voltage with no TxEQ Test 271

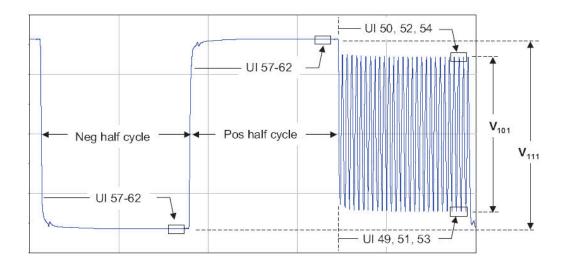

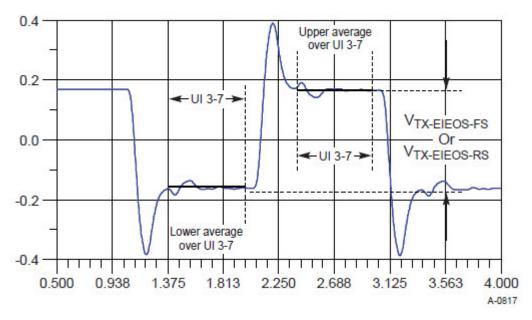

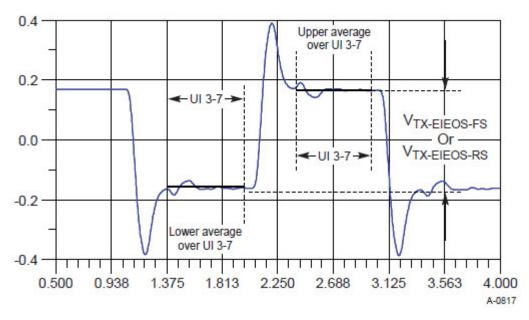

Min Swing During EIEOS for Full Swing Test 273

Min Swing During EIEOS for Reduced Swing Test 276

Uncorrelated Total Jitter Test 279

Uncorrelated Deterministic Jitter Test 280

Total Uncorrelated PWJ (Pulse Width Jitter) Test 281

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 282

Data Dependent Jitter (Information-Only Test) 283

Pseudo Package Loss Test 284

Tx Boost Ratio Full Swing Test 286

Tx Boost Ratio Reduced Swing Test 288

Random Jitter Test 290

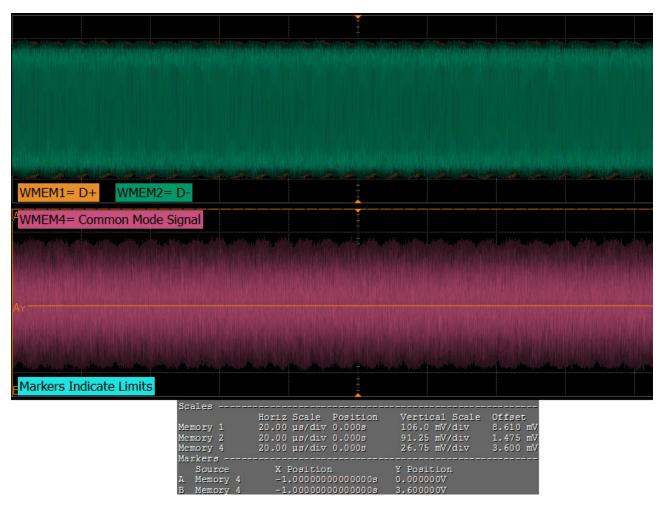

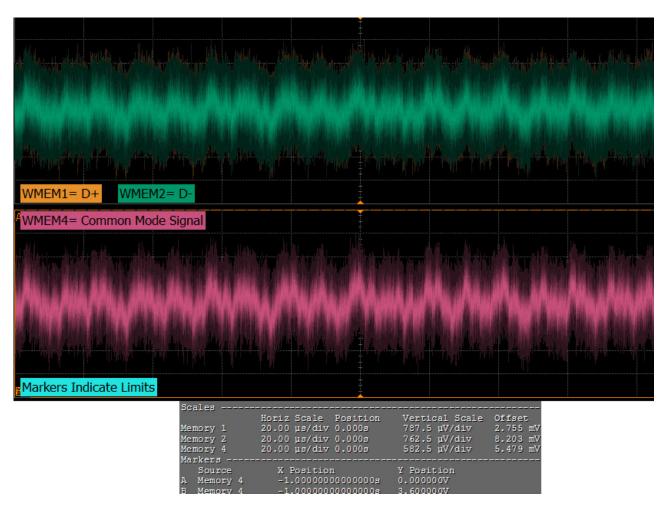

DC Common-Mode Voltage Test 291

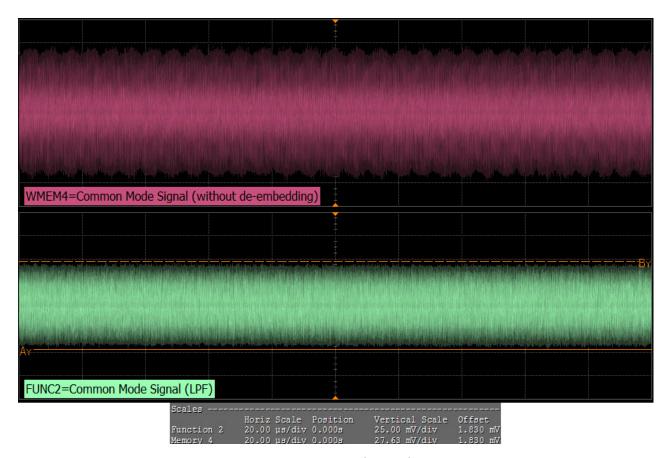

AC Common-Mode Voltage (LPF, 4 GHz) Test 293

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 295

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 297

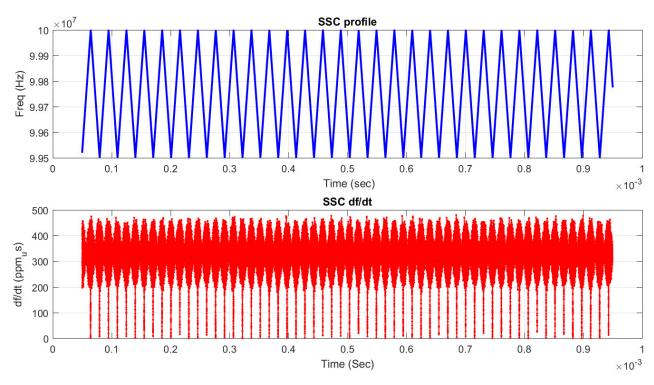

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 299

SSC Modulation Frequency 301

SSC Peak Deviation (Max) 302

SSC Peak Deviation (Min) 303

SSC Max df/dt (Slew Rate) Test 304

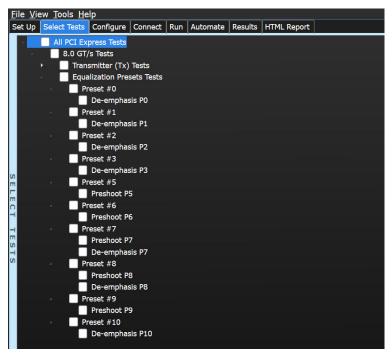

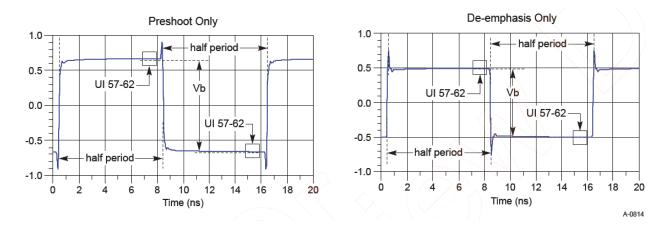

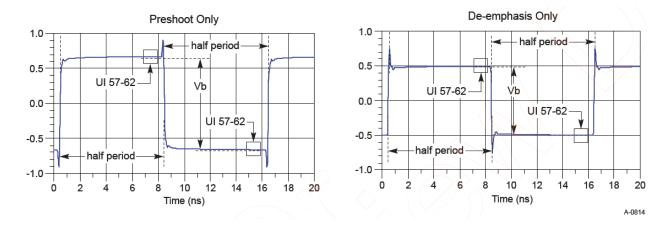

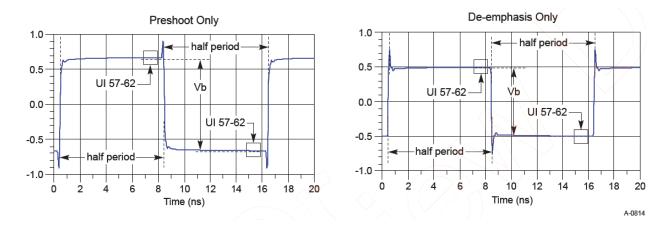

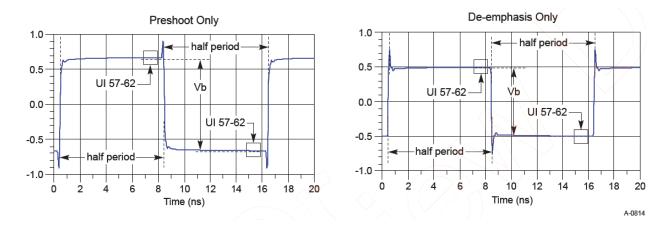

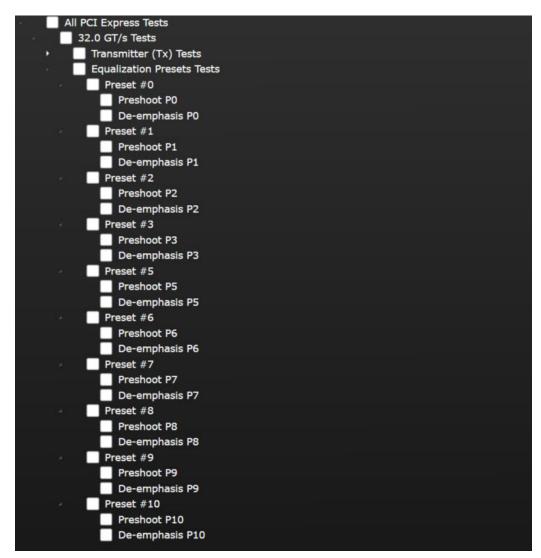

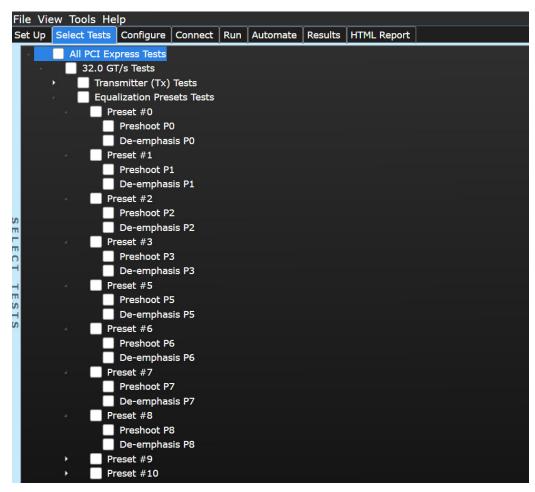

| Running Equalization Presets Tests 306  Preset #0 Measurement (P0), De-emphasis Test 307  Preset #1 Measurement (P1), De-emphasis Test 310  Preset #2 Measurement (P2), De-emphasis Test 313  Preset #3 Measurement (P3), De-emphasis Test 316  Preset #5 Measurement (P5), Preshoot Test 319  Preset #6 Measurement (P6), Preshoot Test 322               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preset #7 Measurement (P7), Preshoot Test 325  Preset #7 Measurement (P7), De-emphasis Test 328  Preset #8 Measurement (P8), Preshoot Test 331  Preset #8 Measurement (P8), De-emphasis Test 333  Preset #9 Measurement (P9), Preshoot Test 336  Preset #10 Measurement (P10), De-emphasis Test 339                                                        |

| 13 CEM-EndPoint Tests, 8.0 GT/s, PCI-E 5.0                                                                                                                                                                                                                                                                                                                 |

| Probing the Link for CEM-EndPoint Compliance 344  Connecting the Compliance Base Board for CEM-EndPoint Testing 344  Running CEM-EndPoint Tests 345  Unit Interval Test (Information Only) 346  Template Tests 348  Eye-Width Test 351  Peak Differential Output Voltage (Transition) Test 354  Peak Differential Output Voltage (Non-Transition) Test 358 |

| 14 CEM-RootComplex Tests, 8.0 GT/s, PCI-E 5.0                                                                                                                                                                                                                                                                                                              |

| Probing the Link for CEM-RootComplex Compliance 362  Connecting the Signal Quality Load Board for System/Motherboard Testing 36                                                                                                                                                                                                                            |

| Running CEM-RootComplex Tests 363  Unit Interval Test (Information Only) 364  Template Tests 366  Peak Differential Output Voltage (Transition) Test 369  Peak Differential Output Voltage (Non-Transition) Test 372  Eye-Width Test 375                                                                                                                   |

| 15 Reference Clock Tests, 8.0 GT/s, PCI-E 5.0                                                                                                                                                                                                                                                                                                              |

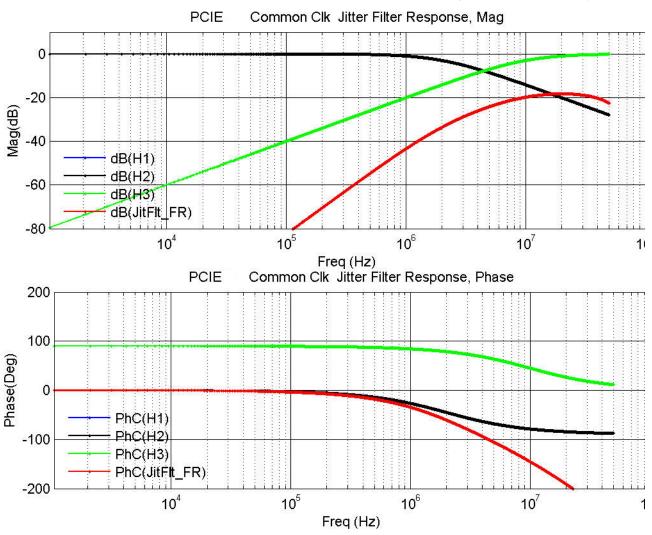

| Reference Clock Architectures 378  Common Clock Architecture 378                                                                                                                                                                                                                                                                                           |

Data Clock Architecture 379

Reference Clock Measurement Point 380

# Running Reference Clock Tests 381

RMS Jitter (Common Clk) Test 382 PCI-SIG Reference Clock Jitter 389

# Part VI

PCI-Express Gen5 16.0 GT/s Tests 391

# 16 Transmitter (Tx) Tests, 16.0 GT/s, PCI-E 5.0

## Tx Compliance Test Load 394

# Running Tx Tests 395

Unit Interval Test 396

Full Swing Tx Voltage with no TxEQ Test 398

Reduced Swing Tx Voltage with no TxEQ Test 400

Min Swing During EIEOS for Full Swing Test 402

Min Swing During EIEOS for Reduced Swing Test 405

Uncorrelated Total Jitter Test 408

Uncorrelated Deterministic Jitter Test 409

Total Uncorrelated PWJ (Pulse Width Jitter) Test 410

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 411

Data Dependent Jitter (Information-Only Test) 412

Pseudo Package Loss Test 413

Tx Boost Ratio Full Swing Test 415

Tx Boost Ratio Reduced Swing Test 417

Random Jitter Test 419

DC Common-Mode Voltage Test 420

AC Common-Mode Voltage (LPF, 8 GHz) Test 422

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 423

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 425

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 427

SSC Modulation Frequency 429

SSC Peak Deviation (Max) 430

SSC Peak Deviation (Min) 431

SSC Max df/dt (Slew Rate) Test 432

## Running Equalization Presets Tests 434

# 17 CEM-EndPoint Tests, 16.0 GT/s, PCI-E 5.0

# Probing the Link for CEM-EndPoint Compliance 436

Connecting the Compliance Base Board for CEM-EndPoint Testing 436

# Running CEM-EndPoint Tests 437

Template Tests 438

Peak Differential Output Voltage (Transition) Test 441

Peak Differential Output Voltage (Non-Transition) Test 444

Eye-Width Test 447

Unit Interval Test (Information Only) 449

Uncorrelated Total PWJ (Pulse Width Jitter) Test 451

Uncorrelated Deterministic Pulse Width Jitter Test (16.0 GT/s) (Information Only) 453

# 18 CEM-RootComplex Tests, 16.0 GT/s, PCI-E 5.0

# Probing the Link for CEM-RootComplex Compliance 456

Connecting the Signal Quality Load Board for System/Motherboard Testing 456

# **Running CEM-RootComplex Tests** 457

Template Tests 458

Peak Differential Output Voltage (Transition) Test 461

Peak Differential Output Voltage (Non-Transition) Test 464

Eye-Width Test 467

Unit Interval Test (Information Only) 469

# 19 Reference Clock Tests, 16.0 GT/s, PCI-E 5.0

**Reference Clock Architectures** 472

Common Clock Architecture 472

Reference Clock Measurement Point 474

Running Reference Clock Tests 475

RMS Jitter (Common Clk) Test 476 PCI-SIG Reference Clock Jitter 480

Part VII PCI Express Gen5 32.0 GT/s Tests 481

20 Transmitter (Tx) Tests, 32.0 GT/s, PCI-E 5.0

Tx Compliance Test Load 484

# Running Tx Tests 485

Unit Interval Test 486

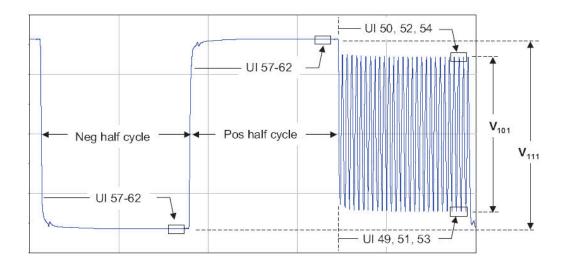

Full Swing Tx Voltage with no TxEQ Test 488

Reduced Swing Tx Voltage with no TxEQ Test 490

Uncorrelated Total Jitter Test 492

Uncorrelated Deterministic Jitter Test 493

Pseudo Package Loss Test 494

Tx Boost Ratio Full Swing Test 496

Tx Boost Ratio Reduced Swing Test 498

Random Jitter 500

Min Swing During EIEOS for Full Swing Test 501

Min Swing During EIEOS for Reduced Swing Test 504

Total Uncorrelated PWJ (Pulse Width Jitter) Test 507

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 508

SSC Modulation Frequency 509

SSC Peak Deviation (Max) 510

SSC Peak Deviation (Min) 511

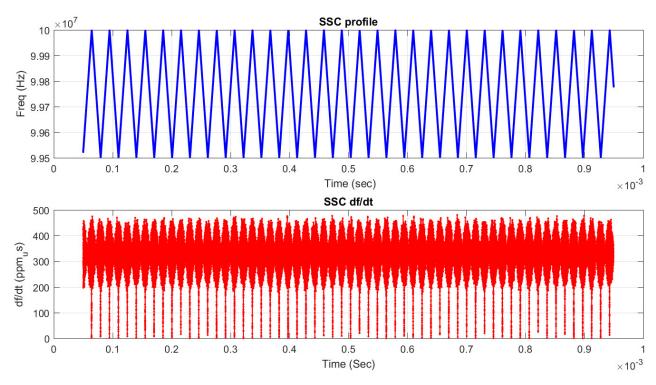

SSC Max df/dt (Slew Rate) Test 512

DC Common-Mode Voltage Test 514

AC Common-Mode Voltage (LPF, 16 GHz) Test 516

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 517

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 519

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 521

# **Running Equalization Presets Tests** 523

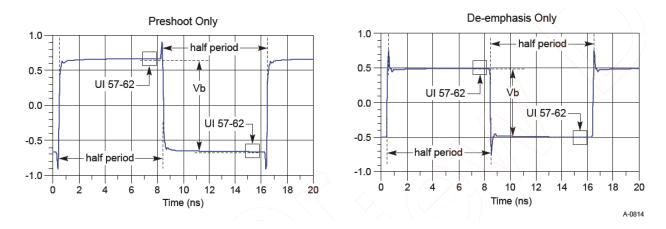

Preset #0 Measurement (P0), Preshoot Test 524

Preset #0 Measurement (P0), De-emphasis Test 528

Preset #1 Measurement (P1), Preshoot Test 531

Preset #1 Measurement (P1), De-emphasis Test 534

Preset #2 Measurement (P2), Preshoot Test 537

Preset #2 Measurement (P2), De-emphasis Test 541

Preset #3 Measurement (P3), Preshoot Test 544

Preset #3 Measurement (P3), De-emphasis Test 547

Preset #5 Measurement (P5), Preshoot Test 550

Preset #5 Measurement (P5), De-emphasis Test 553

Preset #6 Measurement (P6), Preshoot Test 556

Preset #6 Measurement (P6), De-emphasis Test 560

Preset #7 Measurement (P7), Preshoot Test 563

Preset #7 Measurement (P7), De-emphasis Test 566

Preset #8 Measurement (P8), Preshoot Test 569

Preset #8 Measurement (P8), De-emphasis Test 572

Preset #9 Measurement (P9), Preshoot Test 576

Preset #9 Measurement (P9), De-emphasis Test 580

Preset #10 Measurement (P10), Preshoot Test 584

Preset #10 Measurement (P10), De-emphasis Test 587

# 21 CEM-EndPoint Tests, 32.0 GT/s, PCI-E 5.0

# Probing the Link for CEM-EndPoint Compliance 592

Connecting the Compliance Base Board for CEM-EndPoint Testing 592

# **Running CEM-EndPoint Tests** 593

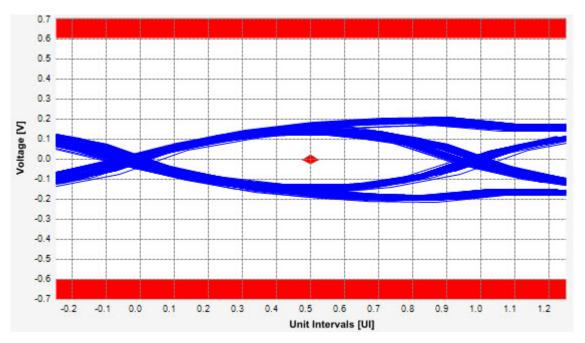

Template Tests 594

Peak Differential Output Voltage (Transition) Test 597

Peak Differential Output Voltage (Non-Transition) Test (Information Only) 600

Eye-Width Test 603

Unit Interval Test (Information Only) 605

Uncorrelated Total Pulse Width Jitter (PWJ) Test 607

Uncorrelated Deterministic Pulse Width Jitter Test (32.0 GT/s) 608

Uncorrelated Total Jitter Test (32.0 GT/s) 609

Uncorrelated Deterministic Jitter Test (32.0 GT/s) 610

# 22 CEM-RootComplex Tests, 32.0 GT/s, PCI-E 5.0

# Probing the Link for CEM-RootComplex Compliance 612

Connecting the Signal Quality Load Board for System/Motherboard Testing 612

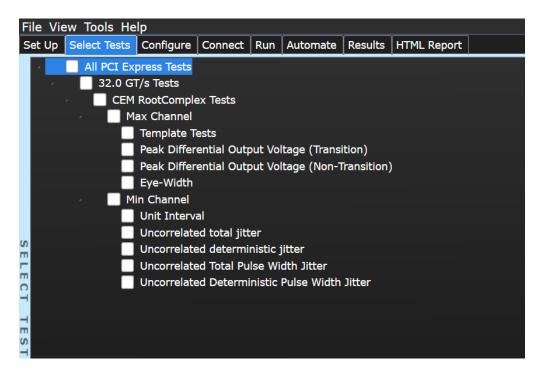

# **Running CEM-RootComplex Tests** 613

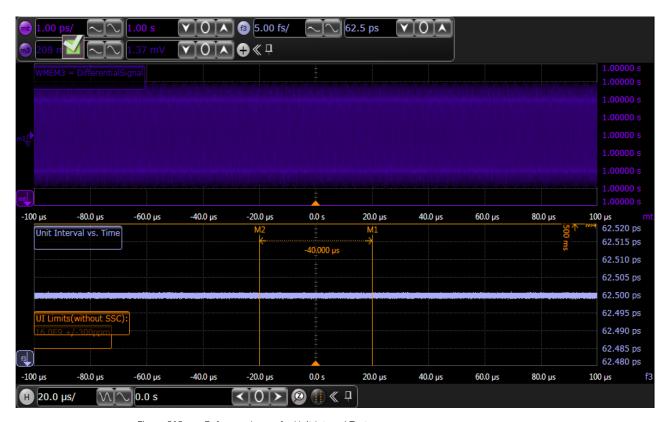

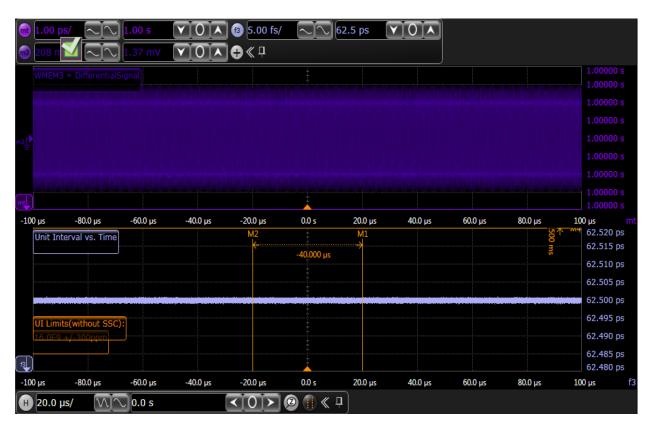

Unit Interval Test (Information Only) 614

Template Tests 616

Peak Differential Output Voltage (Transition) Test (Information Only) 619

Peak Differential Output Voltage (Non-Transition) Test (Information Only) 622

Eye-Width Test (Information Only) 625

Unit Interval Test (Information Only) 627

Uncorrelated Total Jitter Test (32.0 GT/s) 629

Uncorrelated Deterministic Jitter Test (32.0 GT/s) 630

Total Uncorrelated PWJ (Pulse Width Jitter) Test 631

Uncorrelated Deterministic Pulse Width Jitter Test (32.0 GT/s) 632

# 23 Reference Clock Tests, 32.0 GT/s, PCI-E 5.0

#### Reference Clock Architectures 636

Common Clock Architecture 636

# Reference Clock Measurement Point 638

#### Running Reference Clock Tests 639

Average Clock Period Test (32.0 GT/s) 640

RMS Jitter (Common Clk) Test 643

Clock Frequency (Common Clk) Test 648

PCI-SIG Reference Clock Jitter 649

651

# 24 Reference Clock Tests, PCI-E 6.0

#### Reference Clock Measurement Point 654

# Running Reference Clock Tests 655

Rising Edge Rate Test 656

Falling Edge Rate Test 658

Average Clock Period Test 660

Differential Input High Voltage Test 662

Differential Input Low Voltage Test 664

Absolute Crossing Point Voltage Test 666

Duty Cycle Test 668

Variation of V<sub>Cross</sub> Test 670

Clock Frequency (Common Clk) 672

Absolute Max Input Voltage Test 673

Absolute Min Input Voltage Test 675

Rise-Fall Matching Test 677

RefClk SSC Frequency Range (Common Clk) Test 680

RefClk SSC Deviation (Common Clk) Test 681

RefClk Max SSC df/dt (Slew Rate) (Common Clk) Test 682

# Part IX

# PCI-Express Gen6 2.5 GT/s Tests 685

# 25 Transmitter (Tx) Tests, 2.5 GT/s, PCI-E 6.0

#### Tx Compliance Test Load 688

## Running Tx Tests 689

Unit Interval Test 690

Uncorrelated Total Jitter Test 692

Uncorrelated Deterministic Jitter Test 693

SSC Modulation Frequency 694

SSC Peak Deviation (Max) 695

SSC Peak Deviation (Min) 696

SSC df/dt (Max) Test (Slew Rate) 697

DC Common-Mode Voltage Test 699

AC Common-Mode Voltage (LPF, 1.25 GHz) Test 701

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 703

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 705

Deemphasized Voltage Ratio Test 707

Peak Differential Output Voltage (Transition) Test 711

Peak Differential Output Voltage (Non-Transition) Test 715

# 26 Reference Clock Tests, 2.5 GT/s, PCI-E 6.0

#### Reference Clock Architectures 720

Common Clock Architecture 720

Reference Clock Measurement Point 722

Running Reference Clock Tests 723

Peak to Peak Jitter (Common Clk) Test 724

#### Part X

# PCI-Express Gen6 5.0 GT/s Tests 729

# 27 Transmitter (Tx) Tests, 5.0 GT/s, PCI-E 6.0

# Tx Compliance Test Load 732

# Running Tx Tests 733

Unit Interval Test 734

Uncorrelated Total Jitter Test 736

Uncorrelated Deterministic Jitter Test 737

Total Uncorrelated PWJ (Pulse Width Jitter) Test 738

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 739

Random Jitter Test (Information Only Test) 740

SSC Modulation Frequency 741

SSC Peak Deviation (Max) 742

SSC Peak Deviation (Min) 743

SSC df/dt (Max) Test 744

DC Common-Mode Voltage Test 746

AC Common-Mode Voltage (LPF, 2.5 GHz) Test 748

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 749

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 751

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 753

DC Common-Mode Voltage Test 755

AC Common-Mode Voltage (LPF, 1.25 GHz) Test 757

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 759

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 761

Deemphasized Voltage Ratio Test 763

Peak Differential Output Voltage (Transition) Test 767

Peak Differential Output Voltage (Non-Transition) Test 771

# 28 Reference Clock Tests, 5.0 GT/s, PCI-E 6.0

#### Reference Clock Architectures 776

Common Clock Architecture 776

Reference Clock Measurement Point 778

# **Running Reference Clock Tests** 779

RMS Jitter (Common Clk) Test 780

# Part XI

PCI-Express Gen6 8.0 GT/s Tests 785

# 29 Transmitter (Tx) Tests, 8.0 GT/s, PCI-E 6.0

# **Tx Compliance Test Load** 788

# Running Tx Tests 789

Unit Interval Test 790

Full Swing Tx Voltage with no TxEQ Test 793

Reduced Swing Tx Voltage with no TxEQ Test 795

Uncorrelated Total Jitter Test 797

Uncorrelated Deterministic Jitter Test 798

Total Uncorrelated PWJ (Pulse Width Jitter) Test 799

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 800

Pseudo Package Loss Test 801

Tx Boost Ratio Full Swing Test 803

Tx Boost Ratio Reduced Swing Test 805

Random Jitter Test (Information Only) 807

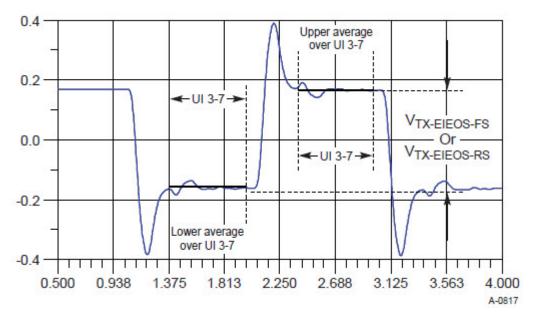

Min Swing During EIEOS for Full Swing Test 808

Min Swing During EIEOS for Reduced Swing Test 811

SSC Modulation Frequency 814

SSC Peak Deviation (Max) 815

SSC Peak Deviation (Min) 816

SSC df/dt (Max) Test 817

DC Common-Mode Voltage Test 819

AC Common-Mode Voltage (LPF, 4 GHz) Test 8:

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 823

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 825

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 827

# **Running Equalization Presets Tests** 829

Preset #0 Measurement (P0), De-emphasis Test 830 833 Preset #1 Measurement (P1), De-emphasis Test Preset #2 Measurement (P2), De-emphasis Test 836 Preset #3 Measurement (P3), De-emphasis Test 839 Preset #5 Measurement (P5), Preshoot Test 842 Preset #6 Measurement (P6), Preshoot Test 845 Preset #7 Measurement (P7), Preshoot Test 848 Preset #7 Measurement (P7), De-emphasis Test 851 Preset #8 Measurement (P8), Preshoot Test 854 Preset #8 Measurement (P8), De-emphasis Test 857 Preset #9 Measurement (P9), Preshoot Test 860 Preset #10 Measurement (P10), De-emphasis Test 863

# 30 Reference Clock Tests, 8.0 GT/s, PCI-E 6.0

#### Reference Clock Architectures 868

Common Clock Architecture 868

Data Clock Architecture 869

Reference Clock Measurement Point 870

Running Reference Clock Tests 87 RMS Jitter (Common Clk) Test 872

# Part XII PCI-Express Gen6 16.0 GT/s Tests 881

31 Transmitter (Tx) Tests, 16.0 GT/s, PCI-E 6.0

Tx Compliance Test Load 884

# Running Tx Tests 885

Unit Interval Test 886

Full Swing Tx Voltage with no TxEQ Test 888

Reduced Swing Tx Voltage with no TxEQ Test 890

Uncorrelated Total Jitter Test 892

Uncorrelated Deterministic Jitter Test 893

Pseudo Package Loss Test 894

Tx Boost Ratio Full Swing Test 896

Tx Boost Ratio Reduced Swing Test 898

Random Jitter Test 900

Min Swing During EIEOS for Full Swing Test 901

Min Swing During EIEOS for Reduced Swing Test 904

Total Uncorrelated PWJ (Pulse Width Jitter) Test 907

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 908

SSC Modulation Frequency 909

SSC Peak Deviation (Max) 910

SSC Peak Deviation (Min) 911

SSC df/dt (Max) Test 912

DC Common-Mode Voltage Test 914

AC Common-Mode Voltage (LPF, 8 GHz) Test 916

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 917

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 919

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 921

# **Running Equalization Presets Tests** 923

# 32 Reference Clock Tests, 16.0 GT/s, PCI-E 6.0

**Reference Clock Architectures** 926

Common Clock Architecture 926

Reference Clock Measurement Point 928

Running Reference Clock Tests 929

RMS Jitter (Common Clk) Test 930

Part XIII

PCI Express Gen6

32.0 GT/s Tests 935

# 33 Transmitter (Tx) Tests, 32.0 GT/s, PCI-E 6.0

Tx Compliance Test Load 938

# Running Tx Tests 939

Unit Interval Test 940

Full Swing Tx Voltage with no TxEQ Test 942

Reduced Swing Tx Voltage with no TxEQ Test 944

Min Swing During EIEOS for Full Swing Test 946

Min Swing During EIEOS for Reduced Swing Test 949

Uncorrelated Total Jitter Test 952

Uncorrelated Deterministic Jitter Test 953

Total Uncorrelated PWJ (Pulse Width Jitter) Test 954

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 955

Pseudo Package Loss Test 956

Tx Boost Ratio Full Swing Test 958

Tx Boost Ratio Reduced Swing Test 960

Random Jitter (Information Only) 962

DC Common-Mode Voltage Test 963

AC Common-Mode Voltage (LPF, 16 GHz) Test 965

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 966

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 968

Absolute Delta of DC Common-Mode Voltage During LO and Idle Test 970

SSC Modulation Frequency 972

SSC Peak Deviation (Max) 973

SSC Peak Deviation (Min) 974

SSC Max df/dt (Slew Rate) Test 975

# **Running Equalization Presets Tests** 977

Preset #0 Measurement (P0), Preshoot Test 978

Preset #0 Measurement (P0), De-emphasis Test 981

Preset #1 Measurement (P1), Preshoot Test 984

Preset #1 Measurement (P1), De-emphasis Test 988

Preset #2 Measurement (P2), Preshoot Test 991

Preset #2 Measurement (P2), De-emphasis Test 994

Preset #3 Measurement (P3), Preshoot Test 997

Preset #3 Measurement (P3), De-emphasis Test 1000

Preset #5 Measurement (P5), Preshoot Test 1003

Preset #5 Measurement (P5), De-emphasis Test 1006

Tieset #3 Measurement (F3), De-emphasis Test

Preset #6 Measurement (P6), Preshoot Test 1009

Preset #6 Measurement (P6), De-emphasis Test 1013

Preset #7 Measurement (P7), Preshoot Test 1016

Preset #7 Measurement (P7), De-emphasis Test 1019

Preset #8 Measurement (P8), Preshoot Test 1022

Preset #8 Measurement (P8), De-emphasis Test 1025

Preset #9 Measurement (P9), Preshoot Test 1028

Preset #9 Measurement (P9), De-emphasis Test 1031

Preset #10 Measurement (P10), Preshoot Test 1034

Preset #10 Measurement (P10), De-emphasis Test 1037

# 34 Reference Clock Tests, 32.0 GT/s, PCI-E 6.0

#### Reference Clock Architectures 1042

Common Clock Architecture 1042

Reference Clock Measurement Point 1043

# Running Reference Clock Tests 1044

Average Clock Period Test (32.0 GT/s) 1046

RMS Jitter (Common Clk) Test 1049

Clock Frequency (Common Clk) Test 1054

Part XIV PCI Express Gen6 64.0 GT/s Tests 1055

# 35 Transmitter (Tx) Tests, 64.0 GT/s, PCI-E 6.0

# Tx Compliance Test Load 1058

# Running Tx Tests 1059

Auto Tune Optimized CTLE (52 UI Jitter Pattern) (Information Only) 1060

Auto Tune Optimized CTLE (PWJ Pattern) (Information Only) 1061

Full Swing Tx Voltage with no TxEQ Test 1062

Reduced Swing Tx Voltage with no TxEQ Test 1064

Pseudo Package Loss Test (Non-Root Device) 1066

Pseudo Package Loss Test (Root Device) 1068

Tx Boost Ratio Full Swing Test 1070

Tx Boost Ratio Reduced Swing Test 1072

Signal to Noise Distortion Ratio Test 1074

Level Separation Mismatch Ratio Test 1076

Min Swing During EIEOS for Full Swing Test 1079

Min Swing During EIEOS for Reduced Swing Test 1082

Uncorrelated Total Jitter Test 1085

Uncorrelated Deterministic Jitter Test 1086

Random Jitter Test (Information Only) 1087

Total Uncorrelated PWJ (Pulse Width Jitter) Test 1088

Deterministic DjDD Uncorrelated PWJ (Pulse Width Jitter) Test 1089

Unit Interval Test 1090

SSC Modulation Frequency 1092

SSC Peak Deviation (Max) 1093

SSC Peak Deviation (Min) 1094

SSC Max df/dt (Slew Rate) Test 1095

DC Common-Mode Voltage Test 1097

AC Common-Mode Voltage (LPF, 16 GHz) Test 1099

AC Common Mode Voltage (BPF, 30 kHz to 500 MHz) Test 1100

Absolute Delta of DC Common Mode Voltage Between D+ and D- Test 1102

Absolute Delta of DC Common-Mode Voltage During L0 and Idle Test 1104

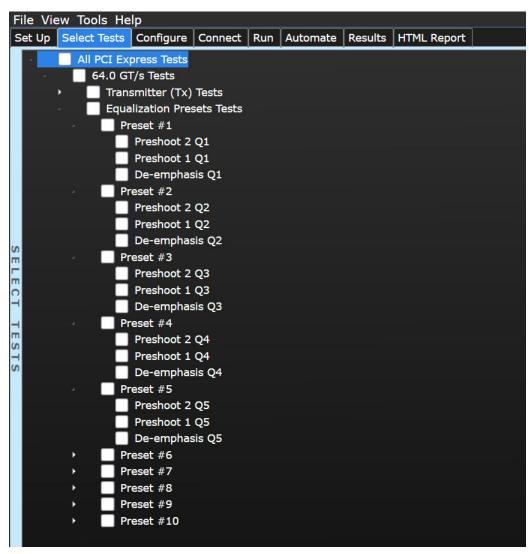

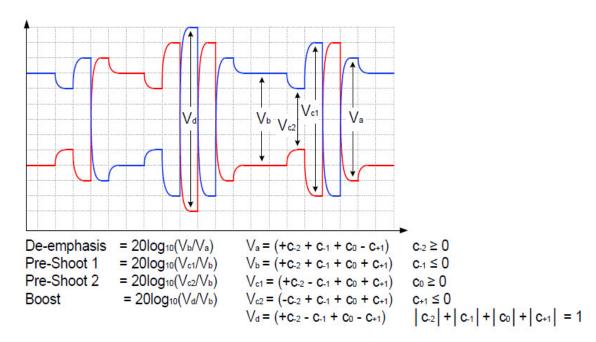

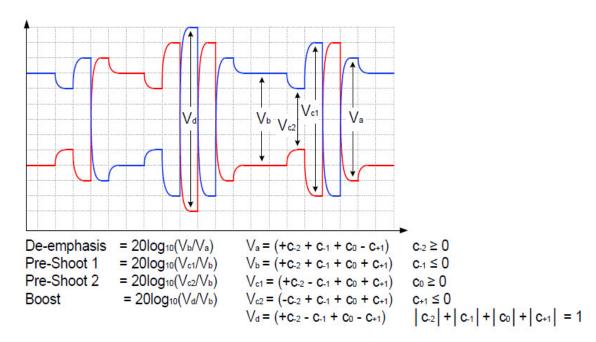

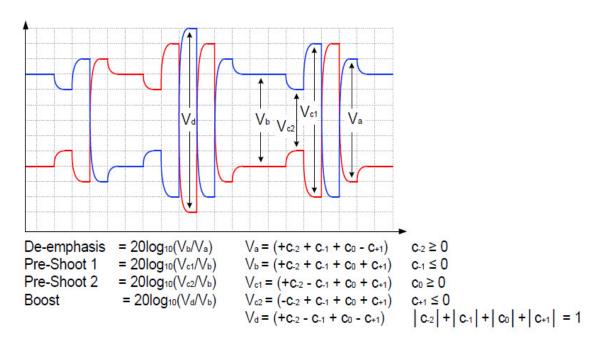

# **Running Equalization Presets Tests** 1106

1107 Preset #1 Measurement (Q1), Preshoot 2 Test Preset #1 Measurement (Q1), Preshoot 1 Test 1110 Preset #1 Measurement (Q1), De-emphasis Test 1112 Preset #2 Measurement (Q2), Preshoot 2 Test 1115 1117 Preset #2 Measurement (Q2), Preshoot 1 Test Preset #2 Measurement (Q2), De-emphasis Test 1119 1122 Preset #3 Measurement (Q3), Preshoot 2 Test 1124 Preset #3 Measurement (Q3), Preshoot 1 Test 1126 Preset #3 Measurement (Q3), De-emphasis Test 1129 Preset #4 Measurement (Q4), Preshoot 2 Test 1131 Preset #4 Measurement (Q4), Preshoot 1 Test Preset #4 Measurement (Q4), De-emphasis Test 1133 Preset #5 Measurement (Q5), Preshoot 2 Test 1136 1139 Preset #5 Measurement (Q5), Preshoot 1 Test Preset #5 Measurement (Q5), De-emphasis Test 1142 1145 Preset #6 Measurement (Q6), Preshoot 2 Test 1148 Preset #6 Measurement (Q6), Preshoot 1 Test Preset #6 Measurement (Q6), De-emphasis Test 1151 1154 Preset #7 Measurement (Q7), Preshoot 2 Test 1157 Preset #7 Measurement (Q7), Preshoot 1 Test Preset #7 Measurement (Q7), De-emphasis Test 1160 Preset #8 Measurement (Q8), Preshoot 2 Test 1163 Preset #8 Measurement (Q8), Preshoot 1 Test 1165 Preset #8 Measurement (Q8), De-emphasis Test 1167 1170 Preset #9 Measurement (Q9), Preshoot 2 Test 1173 Preset #9 Measurement (Q9), Preshoot 1 Test Preset #9 Measurement (Q9), De-emphasis Test 1176 Preset #10 Measurement (Q10), Preshoot 2 Test 1179 Preset #10 Measurement (Q10), Preshoot 1 Test 1182 Preset #10 Measurement (Q10), De-emphasis Test 1185

# 36 Reference Clock Tests, 64.0 GT/s, PCI-E 6.0

Reference Clock Architectures 1190

Common Clock Architecture 1190

Reference Clock Measurement Point 1192

# Running Reference Clock Tests 1193

Average Clock Period Test (64.0 GT/s) 1195 RMS Jitter (Common Clk) Test 1198 Clock Frequency (Common Clk) Test 1203

Part XV Appendices 1205

# A Calibrating the Digital Storage Oscilloscope

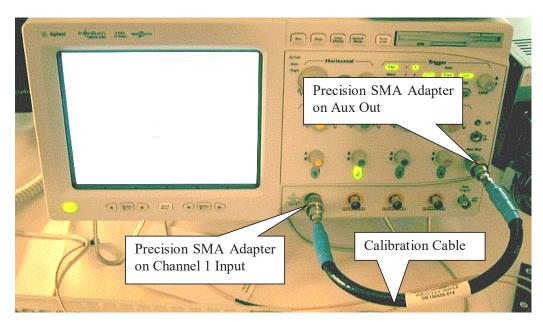

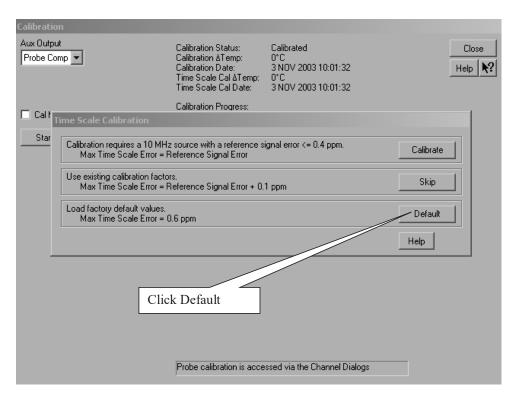

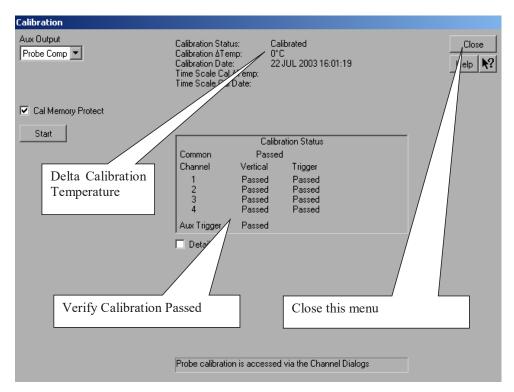

Required Equipment for Calibration 1208

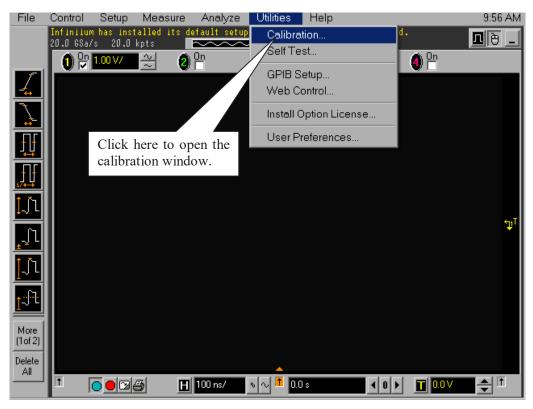

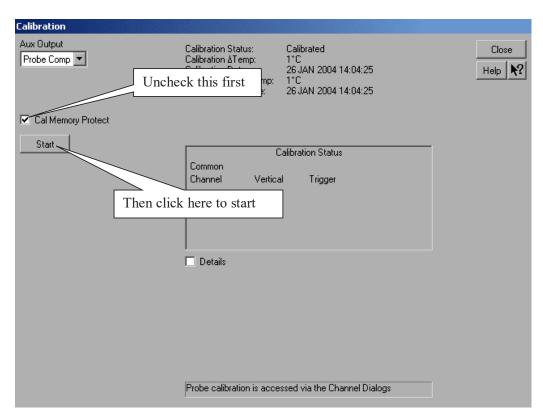

Internal Calibration 1209

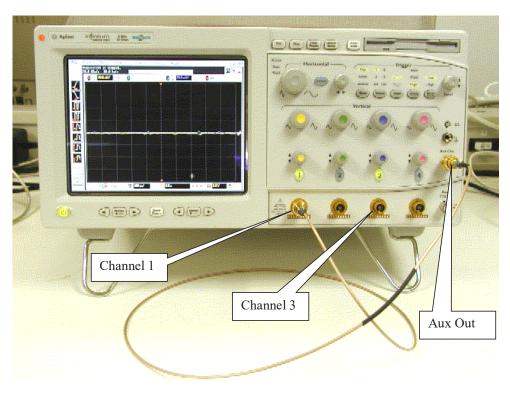

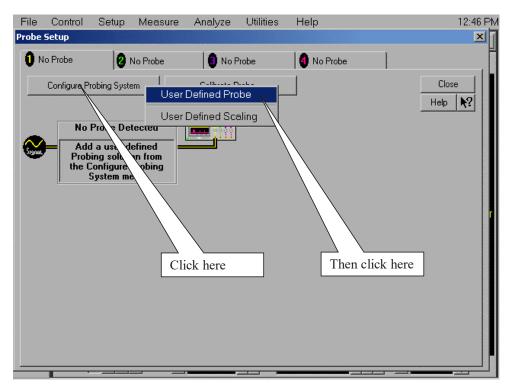

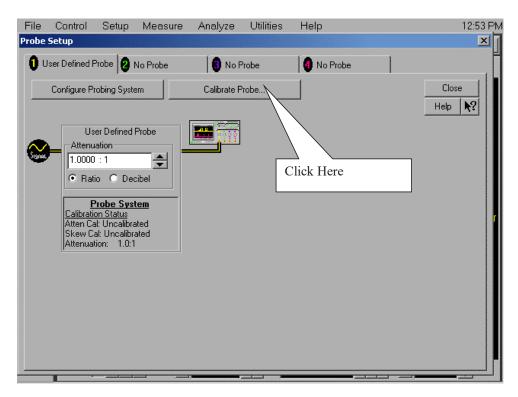

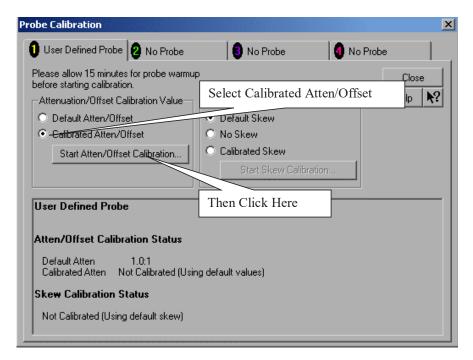

Cable and Probe Calibration 1214

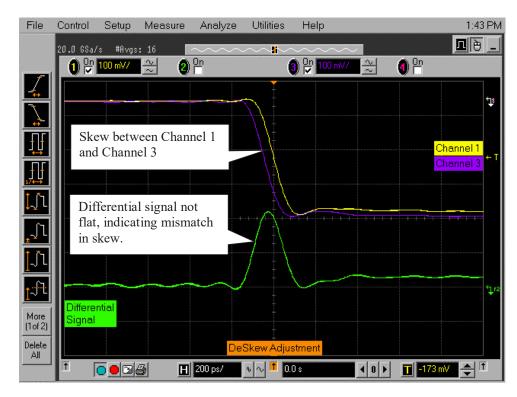

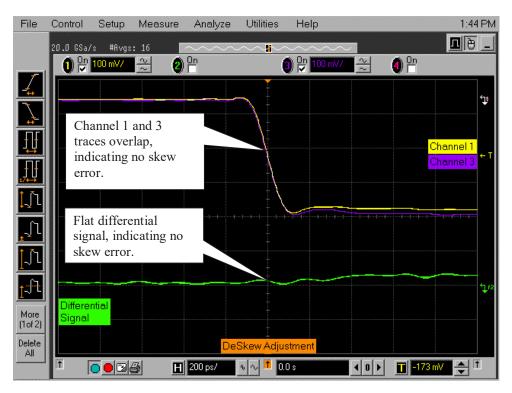

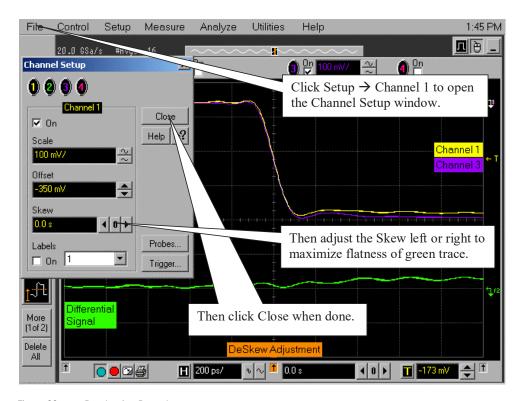

Channel-to-Channel De-skew 1223

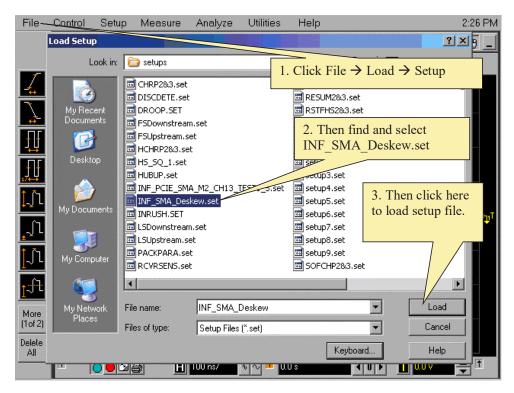

B INF\_SMA\_Deskew.set Setup File Details

C InfiniiMax Probing Options

Index

Contents

| Introduction |

|--------------|

|--------------|

Keysight D9050PCIC PCI Express Compliance Test Application

Methods of Implementation

# 1 Installing the PCI Express Compliance Test Application

Installing the Software / 32

Installing the License Key / 33

If you purchased the D9050PCIC PCI Express Compliance Test Application separately, you need to install the software and license key.

NOTE

D9050PCIC PCI Express Compliance Test Application supports D9010AGGC Compliance Test Software Measurement Server for using multiple machines/PCs over a network as acquisition engines and processing engines in order to significantly enhance the test execution speed. To know more, please see the D9010AGGC product page on keysight.com.

#### 1

# Installing the Software

- 1 Please install the MATLAB Run Time R2021a (9.10). To download please browse the URL: https://in.mathworks.com/products/compiler/matlab-runtime.html

- 2 To obtain the PCI Express Compliance Test Application, please go to Keysight website: http://www.keysight.com/find/D9050PCIC

- 3 The link for PCI Express Compliance Test Application will appear. Double-click on it and follow the instructions to download and install the application software.

- Be sure to accept the installation of the .NET Framework software; it is required in order to run the PCI Express Compliance Test Application.

# Installing the License Key

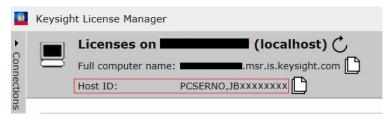

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

Figure 1 Viewing the Host ID information in Keysight License Manager 5

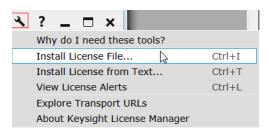

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

- 3 From the configuration menu, use one of the options to install each license file.

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to Keysight License Manager 5 Supporting Documentation.

#### 1

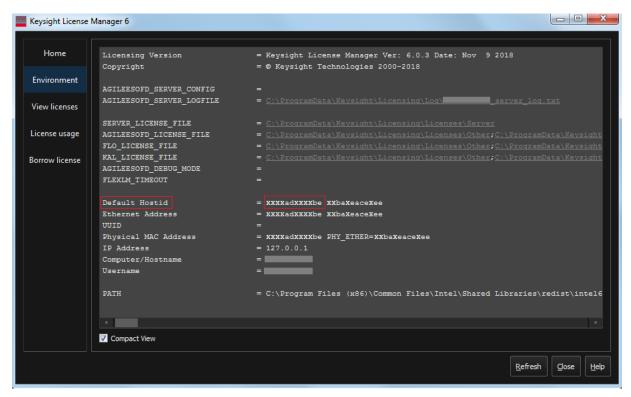

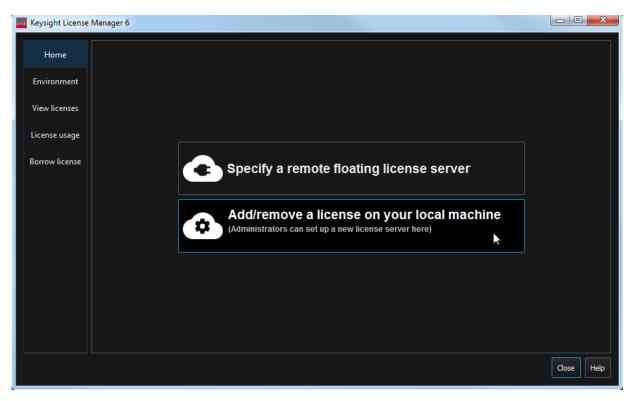

## Using Keysight License Manager 6

To view and copy the Host ID from Keysight License Manager 6:

- 1 Launch Keysight License Manager 6 on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID, which is the first set of alphanumeric value (as highlighted in Figure 3) that appears in the Environment tab of the application. Note that x indicates numeric values.

Figure 3 Viewing the Host ID information in Keysight License Manager 6

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager 6.

- 3 From the Home tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to Keysight License Manager 6 Supporting Documentation.

1 Installing the PCI Express Gen5 Compliance Test Application

Keysight D9050PCIC PCI Express Compliance Test Application

Methods of Implementation

## 2 Preparing to Take Measurements

Calibrating the Oscilloscope / 38 Starting the PCI Express Compliance Test Application / 39

Before running the PCI Express automated tests, you should calibrate the oscilloscope. After the oscilloscope has been calibrated, you are ready to start the PCI Express Compliance Test Application and perform measurements.

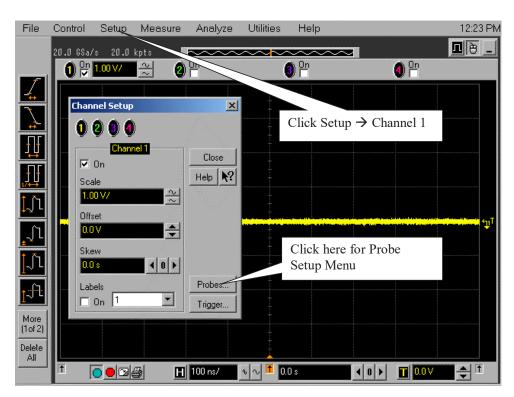

#### Calibrating the Oscilloscope

If you haven't already calibrated the oscilloscope, see Appendix A, "Calibrating the Digital Storage Oscilloscope.

NOTE

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the **Utilities > Calibration** menu.

NOTE

If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration and channel de-skew calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel they were calibrated for.

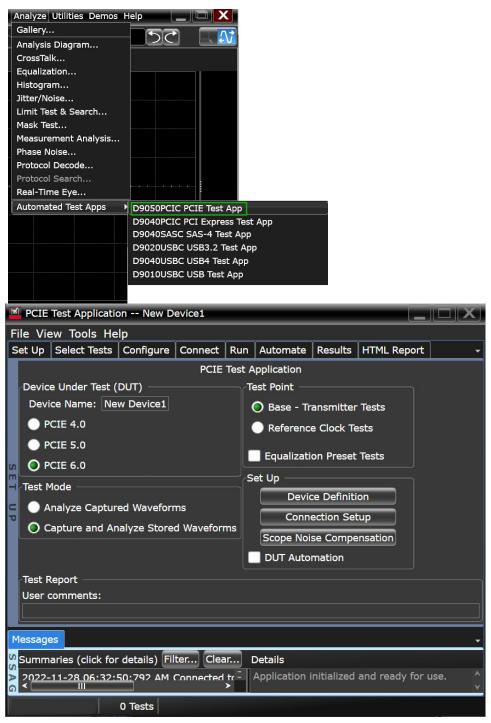

#### Starting the PCI Express Compliance Test Application

1 From the Infiniium oscilloscope's main menu, choose Analyze > Automated Test Apps > D9050PCIC PCIE Test App.

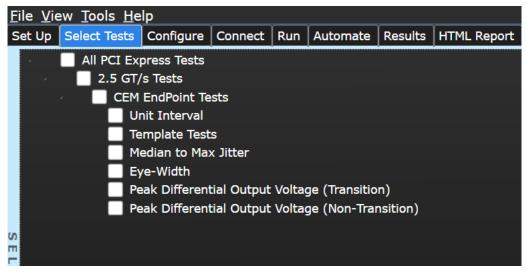

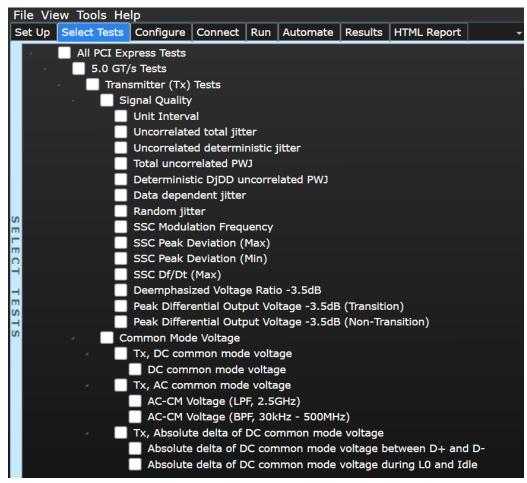

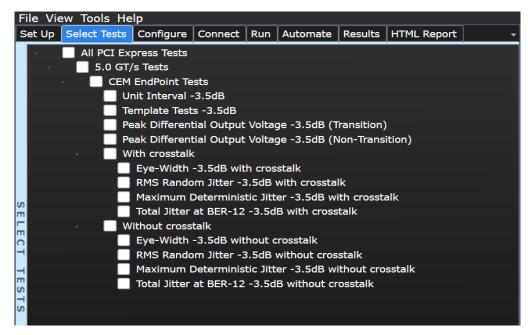

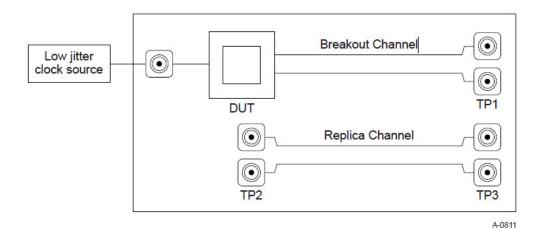

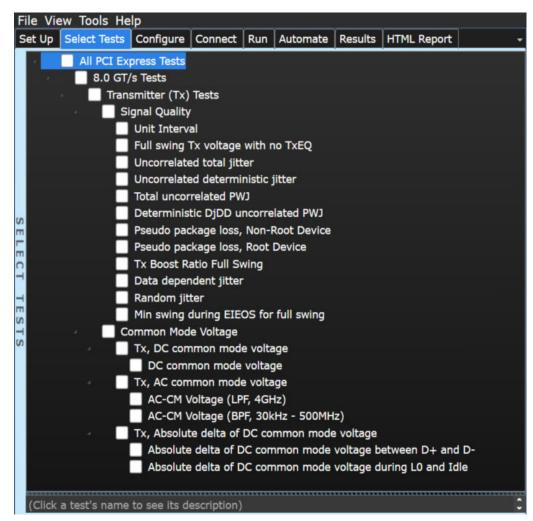

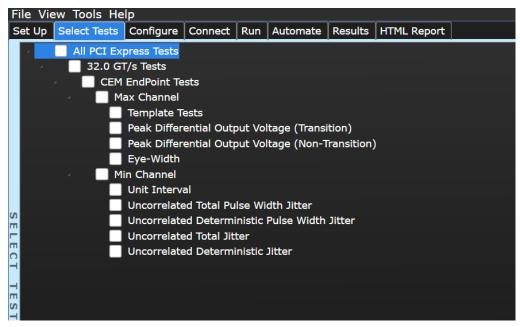

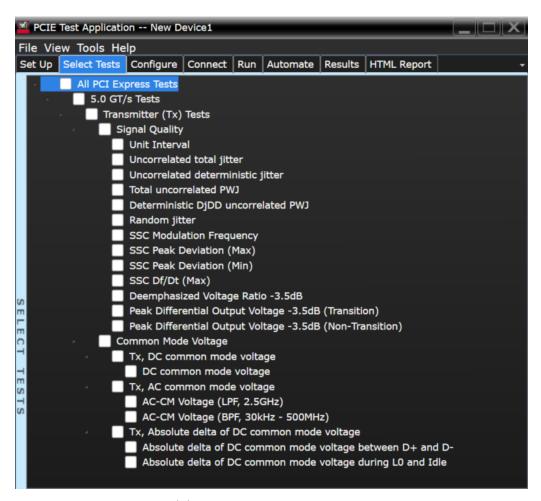

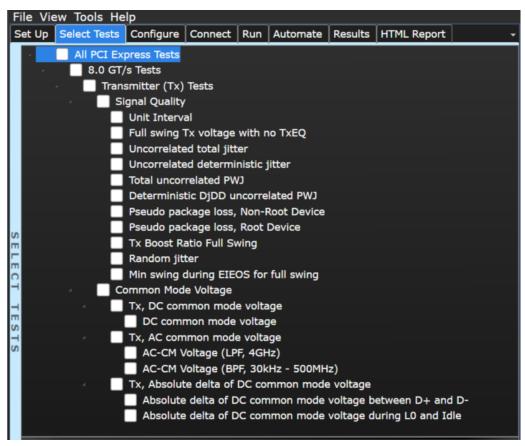

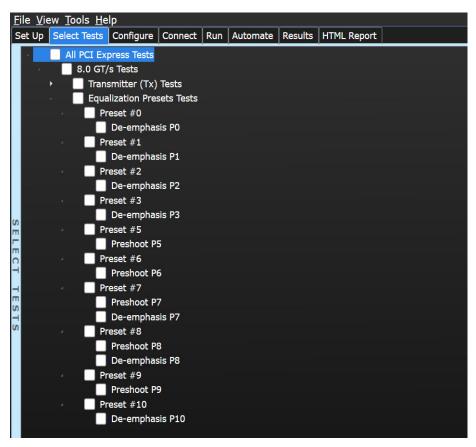

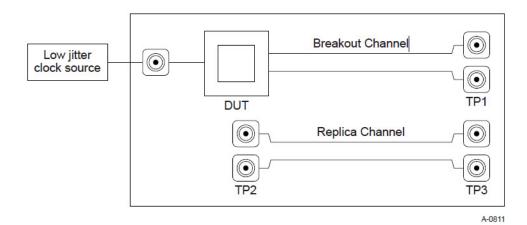

Figure 5 The PCI Express Compliance Test Application

### NOTE

If PCI Express does not appear in the Automated Test Apps menu, the PCI Express Compliance Test Application has not been installed (see Chapter 1, "Installing the PCI Express Compliance Test Application).

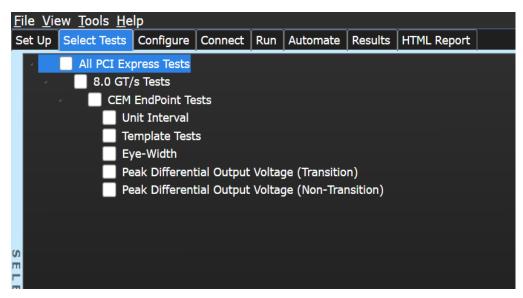

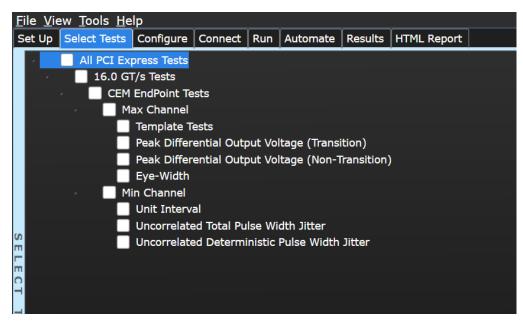

Figure 5 shows the PCI Express Compliance Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Tab          | Description                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Up       | Lets you identify and set up the test environment, including information about the device under test.                                                                                                                                                                      |

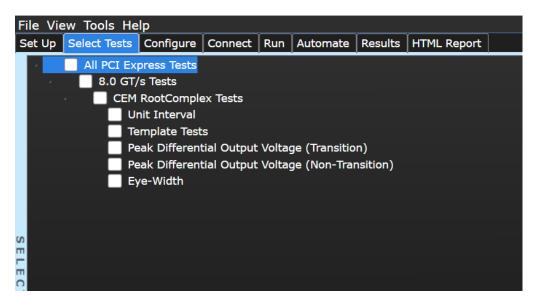

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |

| Configure    | Lets you configure the test parameters (like memory depth). This information appears in the HTML report.                                                                                                                                                                   |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Automate     | Allows to automate tests through automation commands                                                                                                                                                                                                                       |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

#### Online Help Topics

For information on using the PCI Express Compliance Test Application, see its online help (which you can access by choosing Help>Contents... from the application's main menu).

The PCI Express Compliance Test Application's online help describes:

- · Starting the PCI Express Compliance Test Application.

- · To view or minimize the task flow pane.

- To view or hide the toolbar.

- · Creating or opening a test project.

- · Setting up the test environment.

- · To set up InfiniiSim.

- · To load saved waveforms.

- · Selecting tests.

- · Configuring selected tests.

- · Connecting the oscilloscope to the Device Under Test (DUT).

- · Running tests.

- · To select the "store mode".

- · To run multiple times.

- · To send email on pauses or stops.

- · To specify the event.

- · To set the display preferences.

- · To set the run preferences.

- · Viewing test results.

- · To delete trials from the results.

- · To show reference images and flash mask hits.

- · To change margin thresholds.

- · To change the test display order.

- · To set trial display preferences.

- · Viewing/exporting/printing the HTML test report.

- · To export the report.

- To print the report.

- Saving test projects.

- · To set AutoRecovery preferences.

- · Controlling the application via a remote PC.

- · To check for the App Remote license.

- · To identify the remote interface version.

- · To enable the remote interface.

- · To enable remote interface hints.

- · Using a second monitor.

2 Preparing to Take Measurements

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | Part II<br>PCI-Express Gen5<br>All GT/s Tests |

|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----------------------------------------------|

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |                                               |

Keysight D9050PCIC PCI Express Compliance Test Application

Methods of Implementation

# Reference Clock Tests, PCI-E 5.0

Reference Clock Measurement Point / 46 Reference Clock Measurement Point / 46 Running Reference Clock Tests / 47

This section provides the Methods of Implementation (MOIs) for Reference Clock tests, common to all data rates, using Keysight Z-Series or UXR Series Infiniium oscilloscope and the PCI Express Compliance Test Application.

NOTE

In case of Z-series oscilloscope, 32.0 GT/s data rate tests have to use real edge channels in order to support PCI-E 5.0 compliance testing.

NOTE

It is recommended to use normal or non real edge channels on the scope for data rates up to 16.0 GT/s in order to reduce the overall test time.

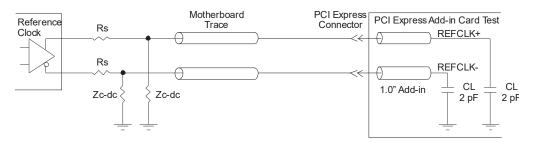

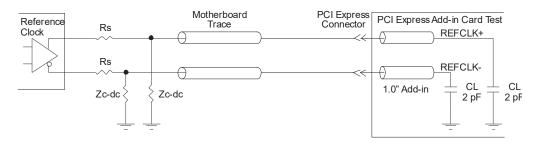

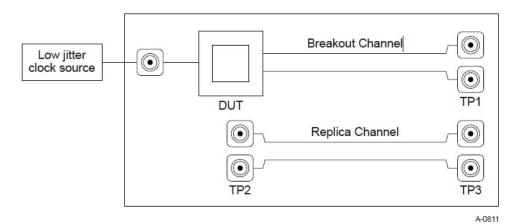

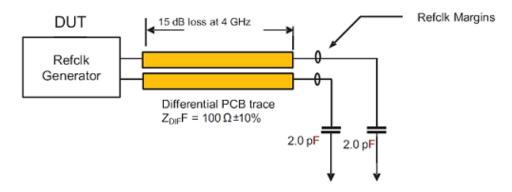

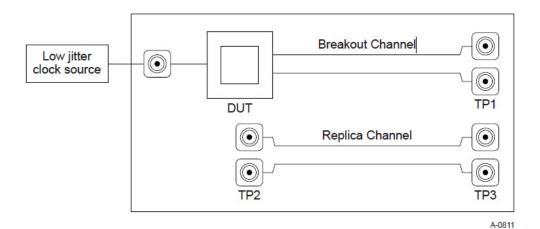

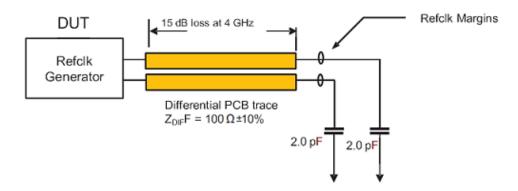

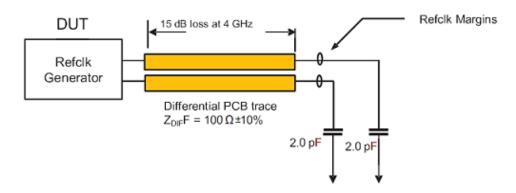

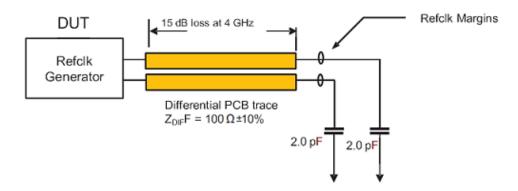

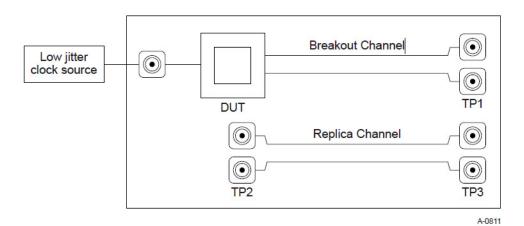

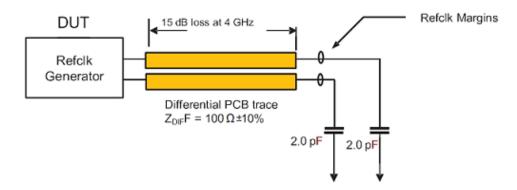

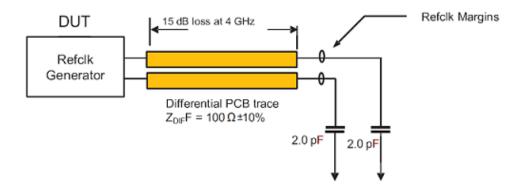

#### Reference Clock Measurement Point

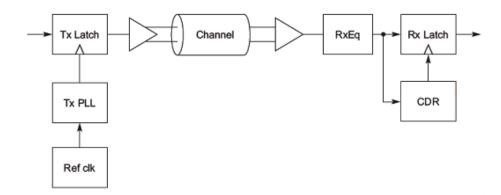

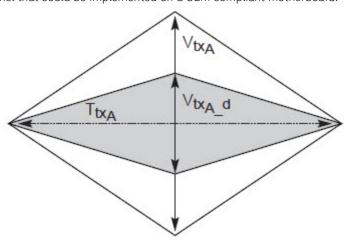

The compliance test load for driver compliance is shown in Figure 4-25 of the PCIe Base Specification.

Figure 1 Driver Compliance Test Load.

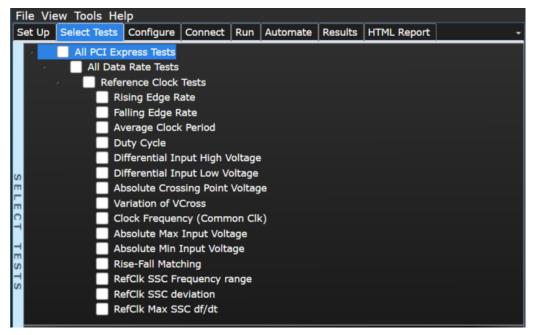

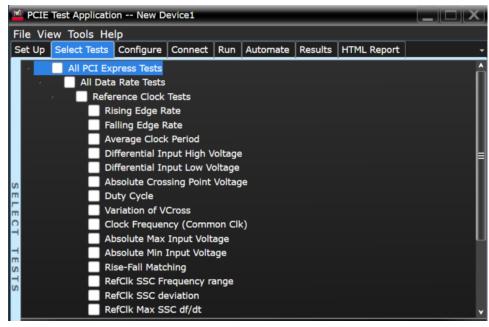

#### Running Reference Clock Tests

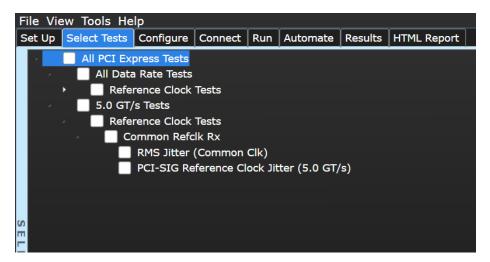

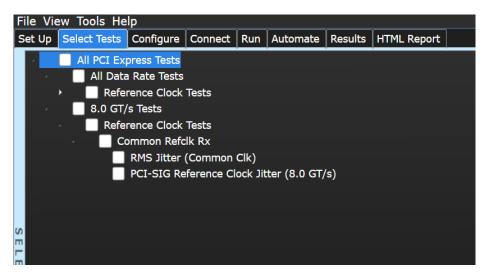

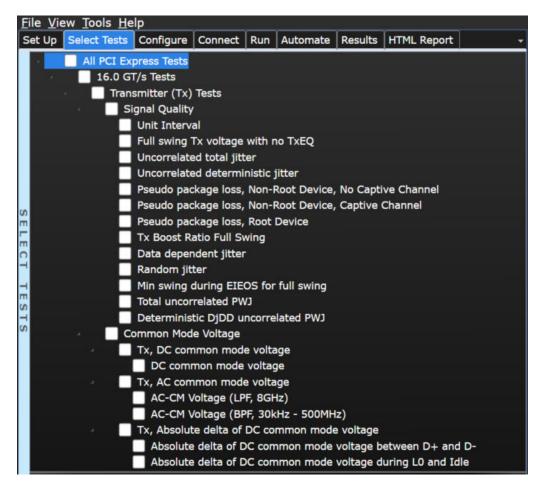

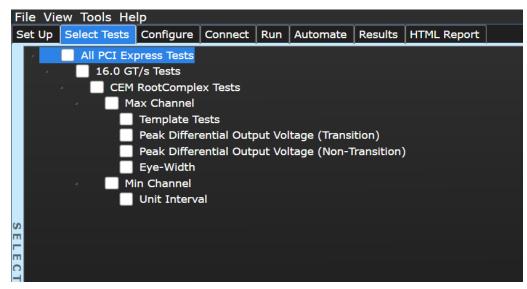

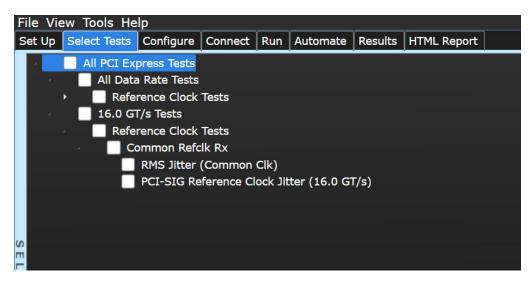

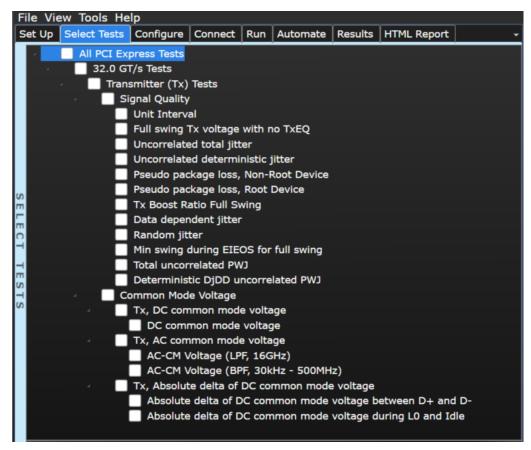

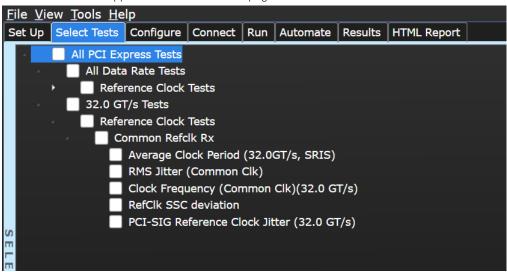

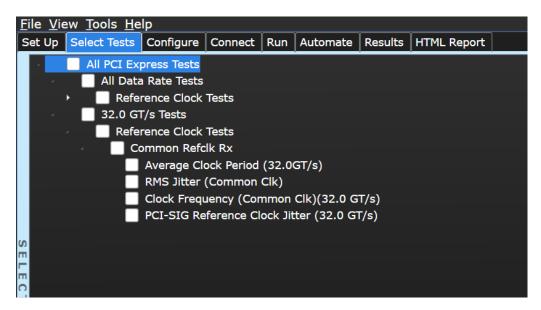

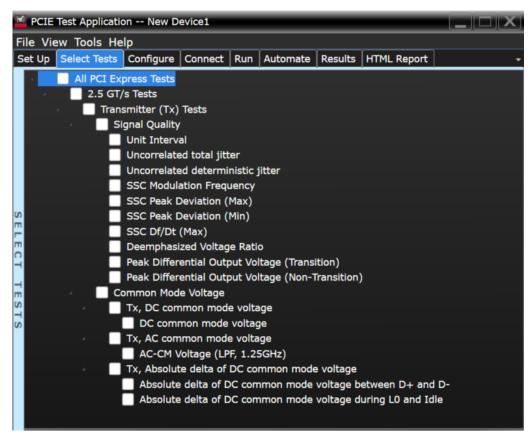

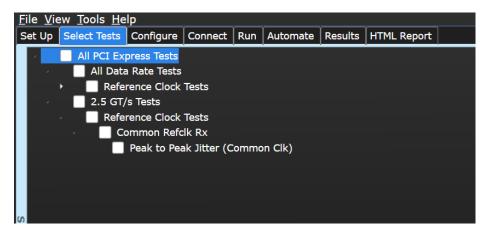

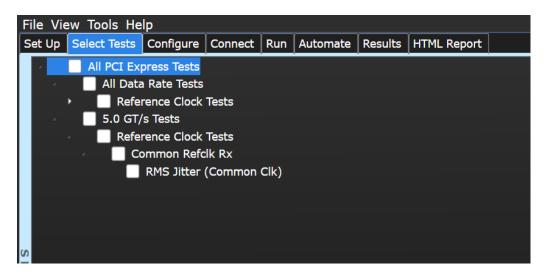

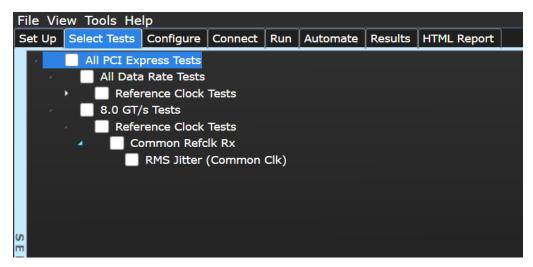

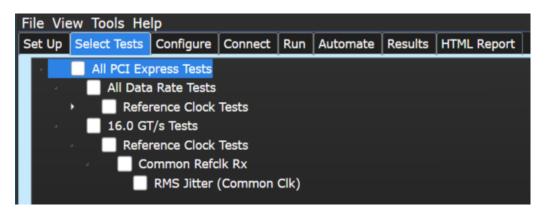

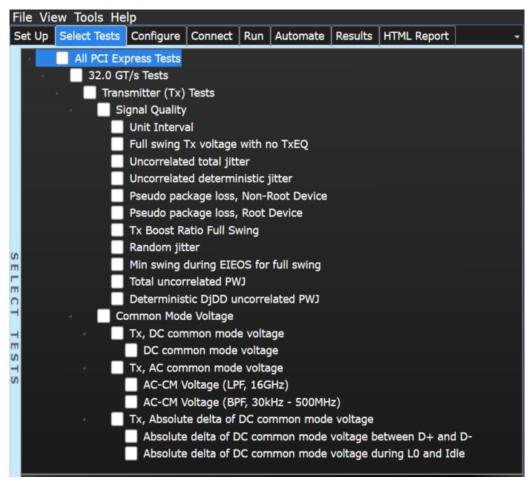

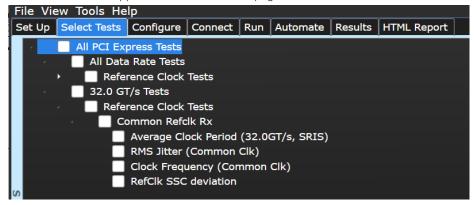

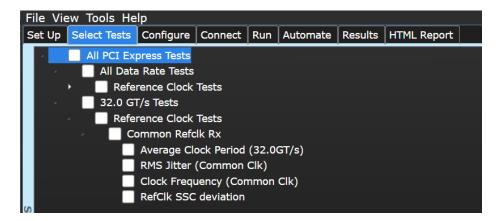

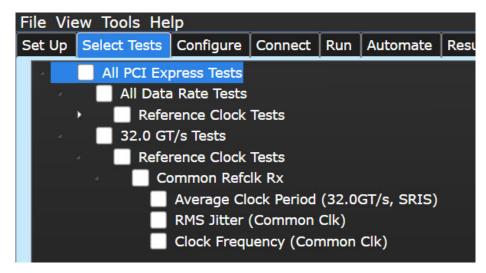

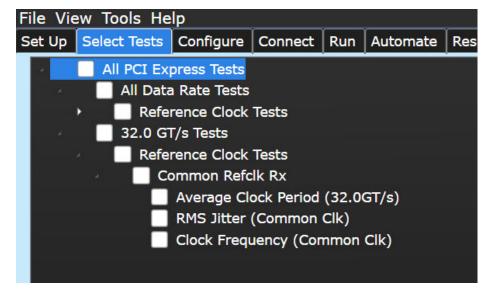

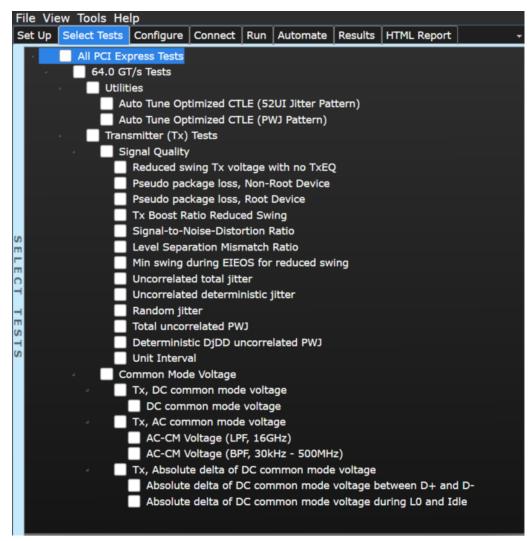

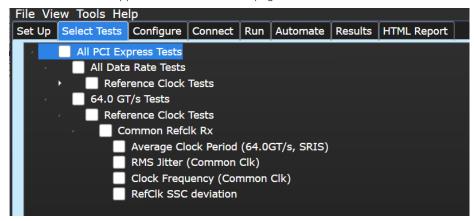

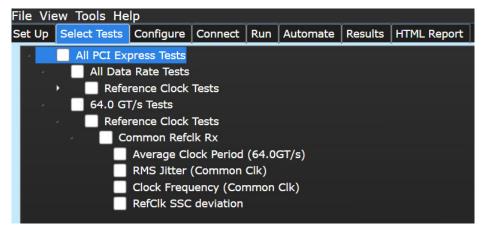

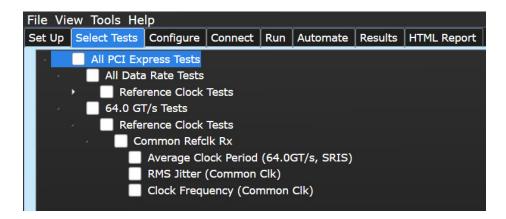

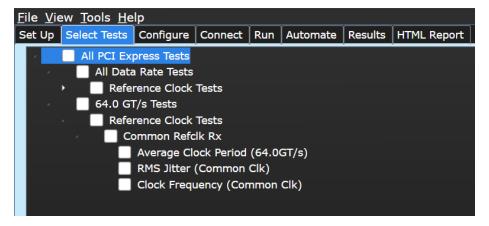

Start the automated testing application as described in "Starting the PCI Express Compliance Test Application" on page 39. Then, when selecting tests, navigate to All PCI Express Tests > All Data Rate Tests > Reference Clock Tests.

Figure 2 Selecting Reference Clock Tests

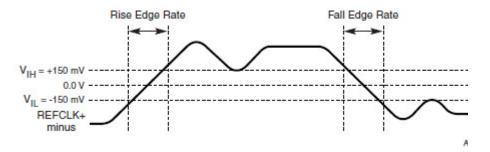

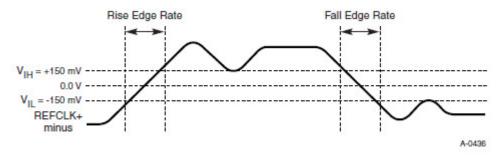

#### Rising Edge Rate Test

The rising edge rate test is measured from -150 mV to +150 mV on the differential waveform which is derived from RefClk+ minus RefClk-. The signal must be monotonic through the measurement region for rise time and 300 mV measurement window is centered on the differential zero crossing.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol         | Parameter        | Min (at 100 MHz Input) | Max (at 100 MHz Input) |

|----------------|------------------|------------------------|------------------------|

| Rise Edge Rate | Rising Edge Rate | 0.6 V/ns               | 4.0 V/ns               |

#### Test Definition Notes from the Specification

- Measurement taken from differential waveform.

- Measured from -150mV to +150mV on the differential waveform (derived from REFCLK+ minus REFCLK-). The signal must be monotonic through the measurement region for rise and fall time.

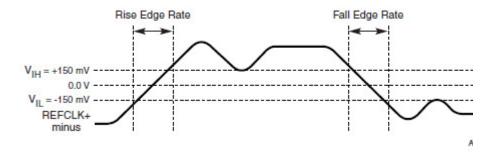

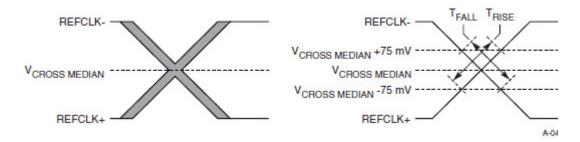

The 300 mV measurement window is centered on the differential zero crossing. See Figure 8-69.

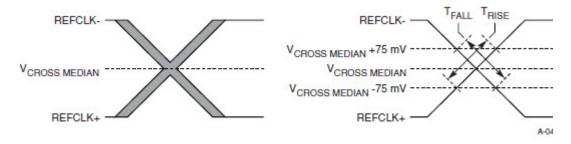

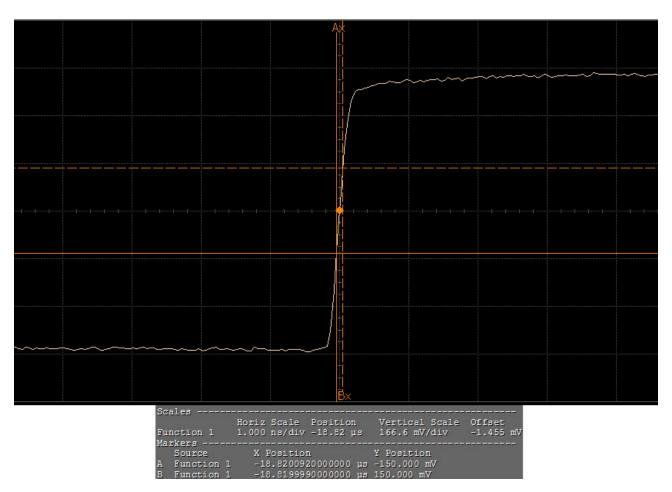

Figure 3 Differential Measurement Points for Rise and Fall Time

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Gets the reference clock signal.

- 2 Configures the value of the test parameters as the values configured for the Number of UI and Sample Rate configuration parameters using Automated Test Engine.

- 3 Fits and displays all sample data on screen.

- 4 Configures the **Top Level** threshold to 150 mV and **Base Level** threshold to -150 mV using **Threshold Setup**.

- 5 Measures the maximum rise time using **Rise time** measurement.

- 6 Zoom to maximum value of rise time.

- 7 Converts the maximum rise time to units of V/ns as given in the PCIE spec. [0.0000000003 / Maximum Rise Time value].

- 8 Reports the rising edge rate value and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 as 0.6  $V/ns \ge Rising Edge Rate \le 4.0 V/ns$ .

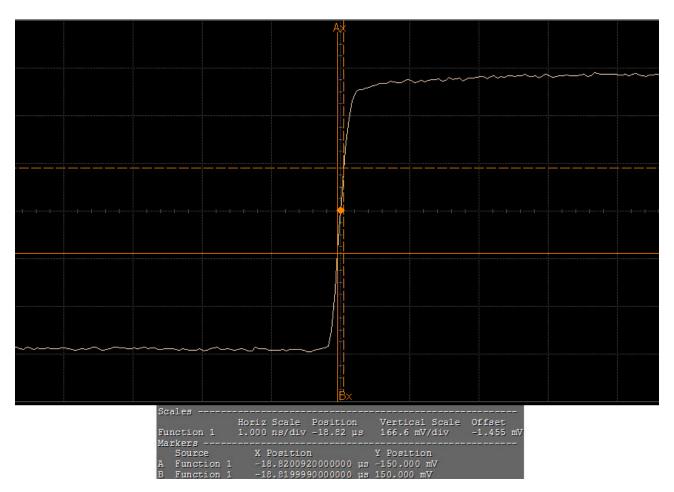

#### Viewing Test Results

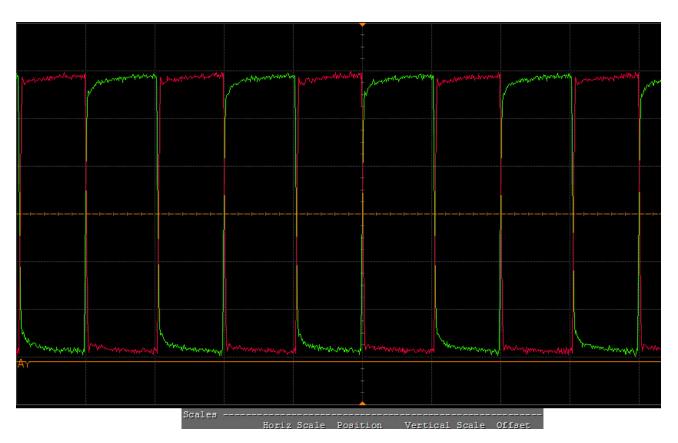

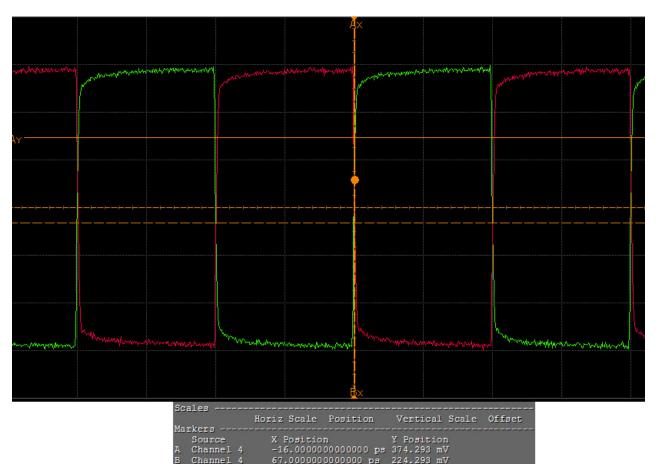

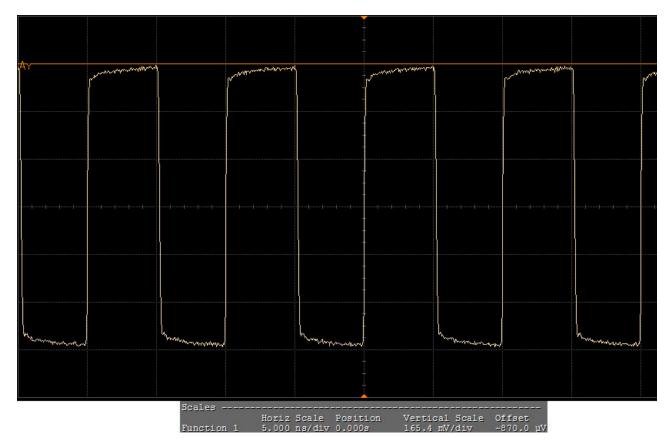

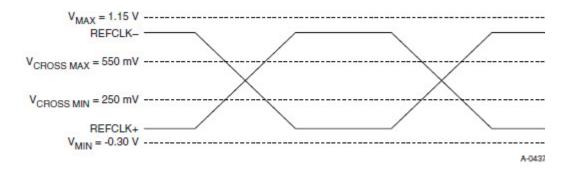

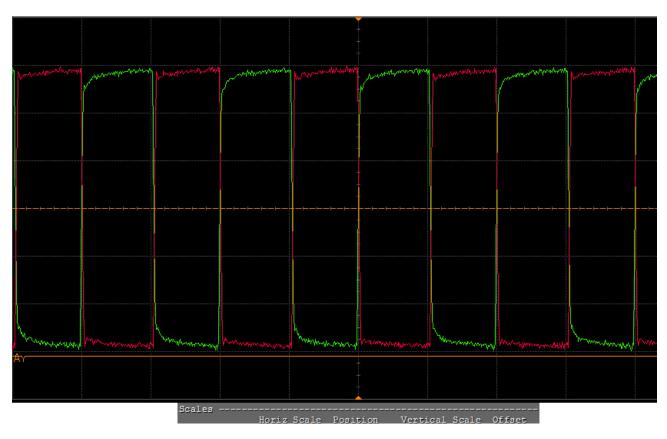

Figure 4 Reference Image for Rising Edge Rate

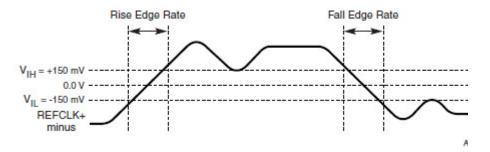

#### Falling Edge Rate Test

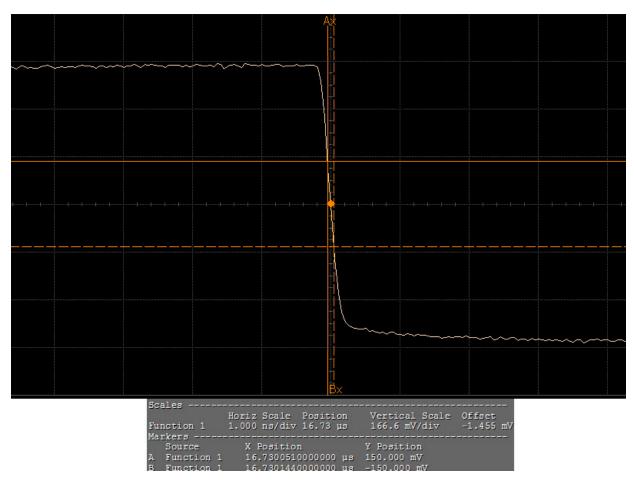

The falling edge rate test is measured from -150 mV to +150 mV on the differential waveform which is derived from RefClk+ minus RefClk-. The signal must be monotonic through the measurement region for fall time and 300 mV measurement window is centered on the differential zero crossing.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol         | Parameter         | Min (at 100 MHz Input) | Max (at 100 MHz Input) |

|----------------|-------------------|------------------------|------------------------|

| Fall Edge Rate | Falling Edge Rate | 0.6 V/ns               | 4.0 V/ns               |

#### Test Definition Notes from the Specification

- Measurement taken from differential waveform.

- Measured from -150 mV to +150 mV on the differential waveform (derived from REFCLK+ minus REFCLK-). The signal must be monotonic through the measurement region for rise and fall time.

The 300 mV measurement window is centered on the differential zero crossing. See, Figure 8-69.

Figure 5 Differential Measurement Points for Rise and Fall Time

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Gets the reference clock signal.

- 2 Configures the value of the test parameters as the values configured for the Number of UI and Sample Rate configuration parameters using Automated Test Engine.

- 3 Fits and displays all sample data on screen.

- 4 Configures the **Top Level** threshold to 150 mV and **Base Level** threshold to -150 mV using **Threshold Setup**.

- 5 Measures the maximum fall time using **Fall time** measurement.

- 6 Zoom the resultant waveform to maximum value of fall time.

- 7 Converts the maximum fall time to units of V/ns as given in the PCIE specification [0.0000000003 / Maximum Fall Time value].

- 8 Reports the falling edge rate value and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 as  $0.6 \text{ V/ns} \le \text{Falling Edge Rate} \le 4.0 \text{ V/ns}$ .

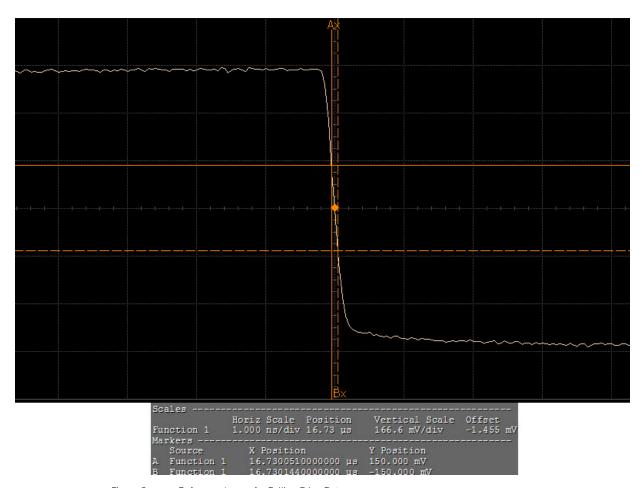

#### Viewing Test Results

Figure 6 Reference Image for Falling Edge Rate

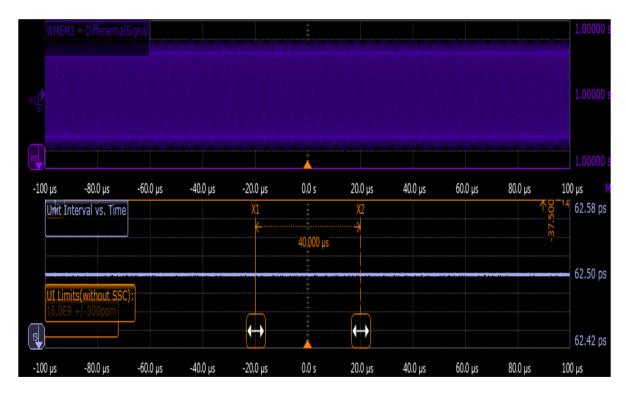

#### Average Clock Period Test

This test verifies that the Refclk Average Clock Period is within the conformance limits as specified in PCIE Express Base Specification, Revision 5.0, Section 8.6.2, Table 8-16.

The average clock period accuracy of the differential waveform is measured in PPM (parts per million) where 1 PPM equals 100 Hz. A requirement of  $\pm$ 00 PPM applies to systems that do not employ SSC or that use a common clock source. For systems employing SSC there is an additional 2500 PPM nominal shift in the maximum period resulting in a maximum average period specification of  $\pm$ 2800 PPM.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol                  | Parameter                     | Min (at 100 MHz Input) | Max (at 100 MHz Input) |

|-------------------------|-------------------------------|------------------------|------------------------|

| T <sub>PERIOD AVG</sub> | Average Clock Period Accuracy | -300 ppm               | 2800 ppm               |

#### Test Definition Notes from the Specification

- · Measurement taken from differential waveform.

- PPM refers to parts per million and is a DC absolute period accuracy specification. 1 PPM is 1/1,000,000th of 100.000000 MHz exactly or 100 Hz. For example for 300 PPM, then we have an error budget of 100 Hz/ PPM × 300 PPM = 30 kHz. The period is to be measured with a frequency counter with measurement window set to 100 ms or greater.

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- Gets the reference clock signal.

- 2 Configures the value of the test parameters as the values configured for the Number of UI and Sample Rate configuration parameters using Automated Test Engine.

- 3 Configures memory depth and sampling rate as per the data rate.

- 4 Fits and displays all sample data on screen.

- 5 Measures the average voltage using **V** average measurement.

- 6 Configures the **Top Level** threshold to +150 mV and **Base Level** threshold to -150 mV using **Threshold Setup**.

- 7 Measures the average frequency using **Frequency** measurement of **Clock**.

- 8 Measures the average period using **Period** measurement of **Clock**.

- 9 Computes the difference between ideal and actual frequency in terms of parts per million of 100MHz as follows:

#### Difference between ideal and actual frequency = [100MHz - AverageFrequency]/100

10 Reports the average clock period accuracy and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16.

NOTE

Base - Reference Clock Tests: MemoryDepth = SamplingRate/100MHz.

#### Viewing Test Results

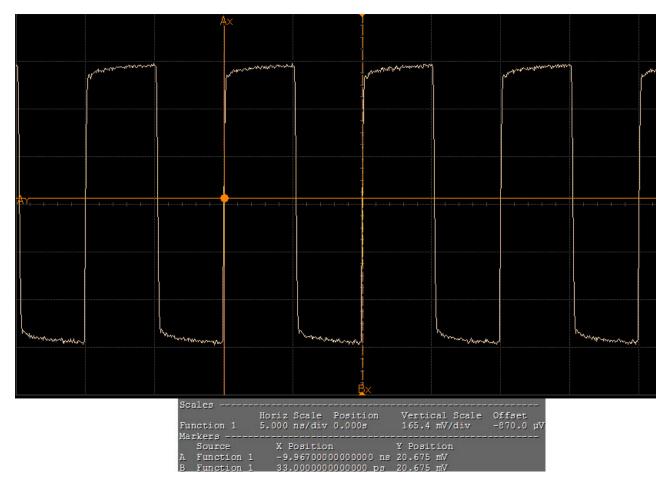

Figure 7 Reference Image for Average Clock Period

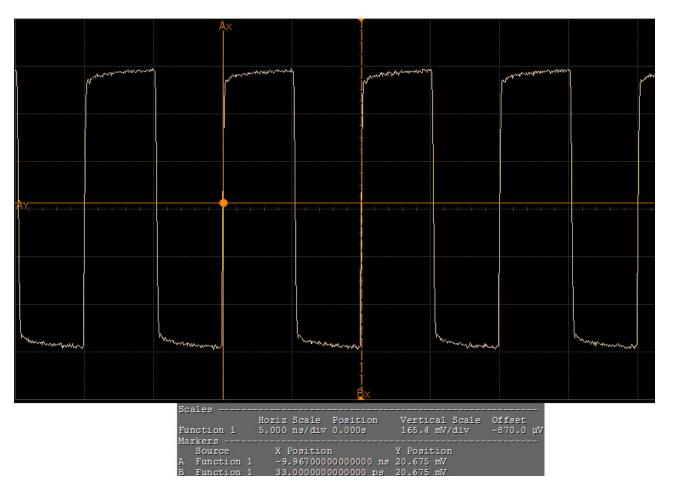

#### Duty Cycle Test

The duty cycle test verifies that the reference clock average clock period is within the conformance limits specified in PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol     | Parameter  | Min (at 100 MHz Input) | Max (at 100 MHz Input) |

|------------|------------|------------------------|------------------------|

| Duty Cycle | Duty Cycle | 40%                    | 60%                    |

#### Test Definition Notes from the Specification

Measurement taken from differential waveform.

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Gets the reference clock signal.

- 2 Configures the value of the test parameters as the values configured for the Number of UI and Sample Rate configuration parameters using Automated Test Engine.

- 3 Configures memory depth and sampling rate as per the data rate.

- 4 Fits and displays all sample data on screen.

- 5 Measures the average voltage using **V** average measurement.

- 6 Configures the **Top Level** threshold to 150 mV and **Base Level** threshold to -150 mV using **Threshold Setup**.

- 7 Measures the duty cycle using the **Duty cycle** measurement.

- 8 Finds the margin for maximum duty cycle and minimum duty cycle.

- 9 Compares the margin and choose the largest margin to report the value (worst value) as duty cycle.

- 10 Reports the measurement results and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 as 40% ≤ Duty Cycle ≤ 60%.

NOTE

Base - Reference Clock Tests: MemoryDepth = SamplingRate/100MHz.

#### Viewing Test Results

Figure 8 Reference Image for Duty Cycle

#### Differential Input High Voltage Test

The differential input high voltage test verifies that the reference clock differential input high voltage is within the conformance limits specified in PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol          | Parameter                       | Min (at 100 MHz Input) |

|-----------------|---------------------------------|------------------------|

| V <sub>IH</sub> | Differential Input High Voltage | 150 mV                 |

#### Test Definition Notes from the Specification

Measurement taken from differential waveform.

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Gets the reference clock signal.

- 2 Configures the value of the test parameters as the values configured for the **Number of UI** and **Sample Rate** configuration parameters using Automated Test Engine.

- 3 Fits and displays all sample data on screen.

- 4 Configures the **Top Level** threshold to 150 mV and **Base Level** threshold to -150 mV using **Threshold Setup**.

- 5 Measures the maximum voltage using **V max** measurement.

- Reports the maximum voltage value as differential input high voltage and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 as  $V_{IH} > 150$  mV.

#### Viewing Test Results

Figure 9 Reference Image for Differential Input High Voltage Test

#### Differential Input Low Voltage Test

The differential input low voltage test verifies that the reference clock differential input low voltage is within the conformance limits specified in PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol          | Parameter                       | Max (at 100 MHz Input) |

|-----------------|---------------------------------|------------------------|

| V <sub>IL</sub> | Differential Input High Voltage | -150 mV                |

#### Test Definition Notes from the Specification

· Measurement taken from differential waveform.

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Gets the reference clock signal.

- 2 Configures the value of the test parameters as the values configured for the **Number of UI** and **Sample Rate** configuration parameters using Automated Test Engine.

- 3 Fits and displays all sample data on screen.

- 4 Configures the **Top Level** threshold to 150 mV and **Base Level** threshold to -150 mV using **Threshold Setup**.

- 5 Measures the minimum voltage using **V min** measurement.

- Reports the minimum voltage value as differential input low voltage and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Card Electromechanical Specification Rev. 1.1 as  $V_{\rm H}$  < 150 mV.

#### Viewing Test Results

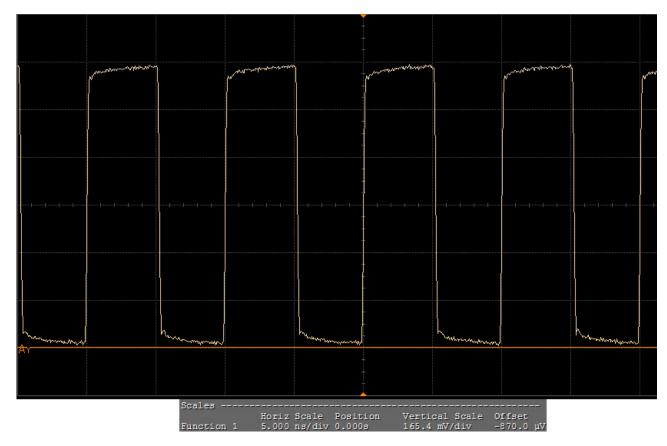

Figure 10 Reference Image for Differential Input Low Voltage Test

#### Absolute Crossing Point Voltage Test

The absolute crossing point voltage test is measured at crossing point where the instantaneous voltage value of the rising edge of RefClk+ equals the falling edge of RefClk-. It refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing.

#### Test Reference

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

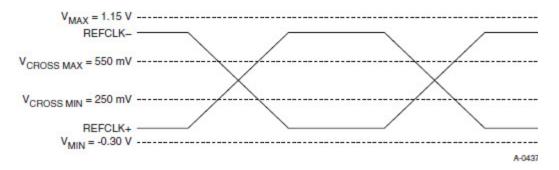

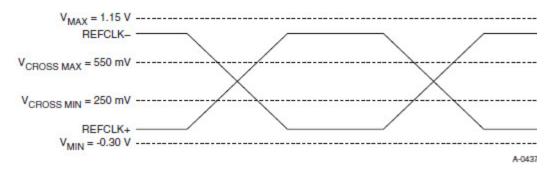

#### Test Definition Notes from the Specification

Table 1

Absolute Crossing Point Voltage Test Details

| Symbol             | Parameter                       | Min( at 100 MHz Input) | Max (at 100 MHz Input) |

|--------------------|---------------------------------|------------------------|------------------------|

| V <sub>CROSS</sub> | Absolute Crossing Point Voltage | +250 mV                | +550 mV                |

- Measurement taken from single ended waveform.

- Measured at crossing point where the instantaneous voltage value of the rising edge of REFCLK+ equals the falling edge of REFCLK-. See Figure 8-65.

- Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement. See Figure 8-65.

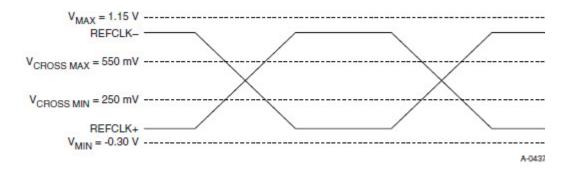

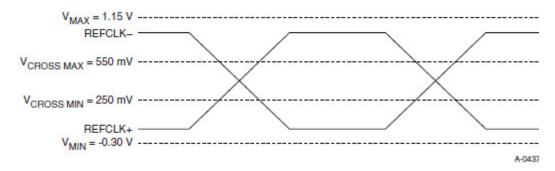

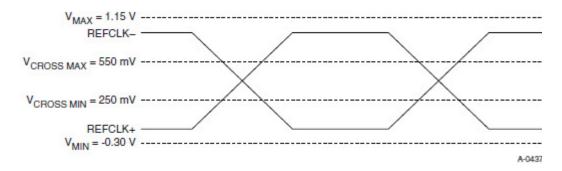

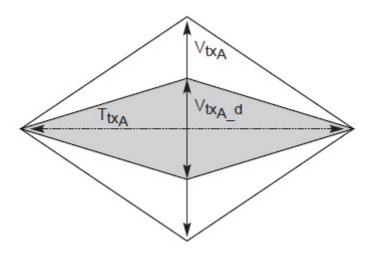

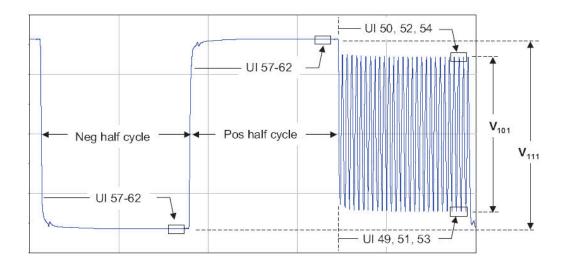

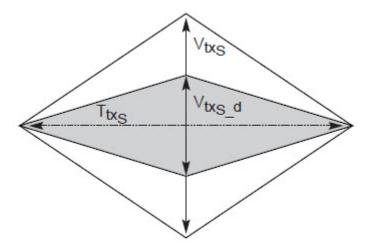

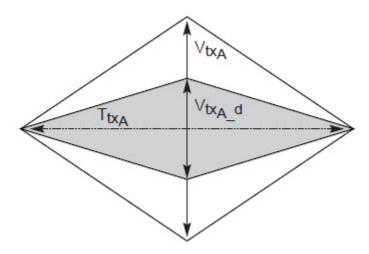

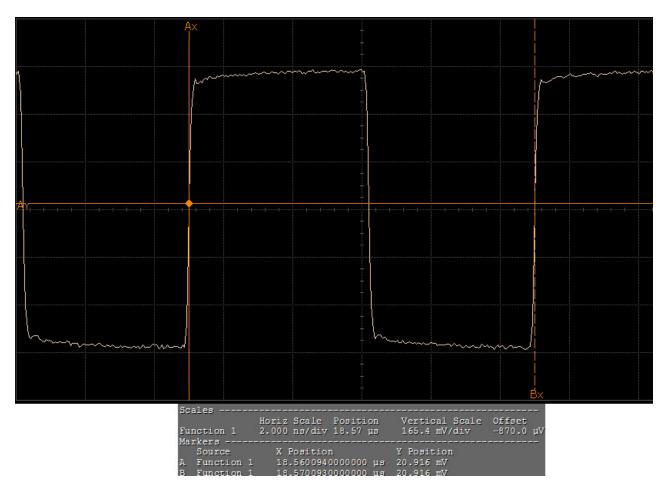

Figure 11 Single-Ended Measurement Points for Absolute Cross Point and Swing

#### Understanding the Test Flow

NOTE

Before executing the test, ensure that the DUT is transmitting compliance test pattern defined in section 4.2.10 of the PCI Express Base Specification.

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Configures the value of the test parameters as the values configured for the **Number of UI** and **Sample Rate** configuration parameters using Automated Test Engine.

- 2 Fits and displays all sample data on screen.

- 3 Uses MATLAB function to find the absolute crossing point voltage. The MATLAB function does the following:

- a Finds crossing edges for rising and falling edges.

- b Finds delta crossing for rising edge of RefClk+ and falling edge of RefClk-.

- 4 Computes the margin for minimum crossing point voltage and margin of maximum crossing point voltage.

- 5 Compares the margin and choose the smallest margin to report the value (worst value) as absolute crossing point voltage.

- 6 Reports the measurement results and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 as 250mV ≤ Absolute Crossing Point Voltage ≤ 550mV.

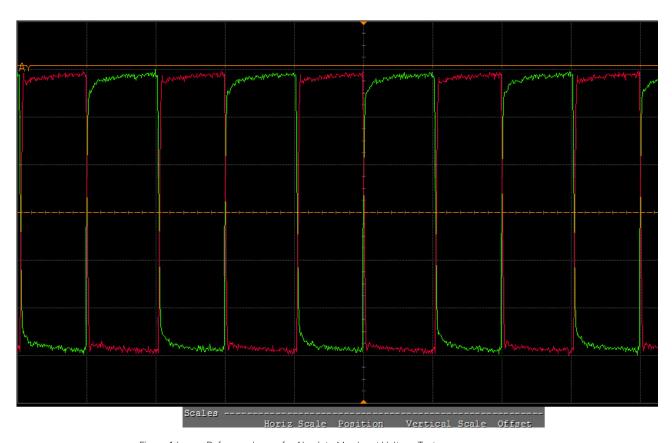

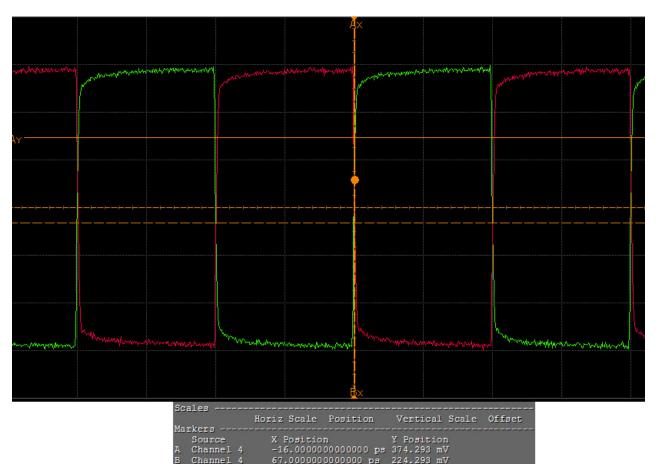

#### Viewing Test Results

#### Variation of V<sub>Cross</sub> Test

The variation of  $V_{Cross}$  test is measured at crossing point where the instantaneous voltage value of the rising edge of Refclk+ equals the falling edge of Refclk-. It is defined as the total variation of all voltages of rising Refclk+ and falling Refclk-.

#### **Test Reference**

PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 is used as reference to check the compliance of the DUT.

| Symbol                   | Parameter                                                                  | Max (at 100 MHz Input) |

|--------------------------|----------------------------------------------------------------------------|------------------------|

| V <sub>CROSS</sub> Delta | Variation of $V_{\mbox{\footnotesize{CROSS}}}$ over all rising clock edges | +140 mV                |

#### Test Definition Notes from the Specification

- Measurement taken from single ended waveform.

- Measured at crossing point where the instantaneous voltage value of the rising edge of REFCLK+ equals the falling edge of REFCLK-. See Figure 8-65.

- Defined as the total variation of all crossing voltages of Rising REFCLK+ and Falling REFCLK-.

This is the maximum allowed variance in V<sub>CROSS</sub> for any particular system. See Figure 8-66.

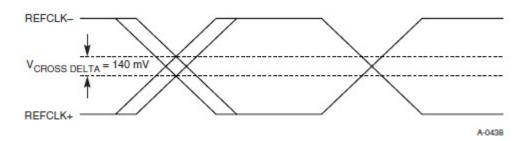

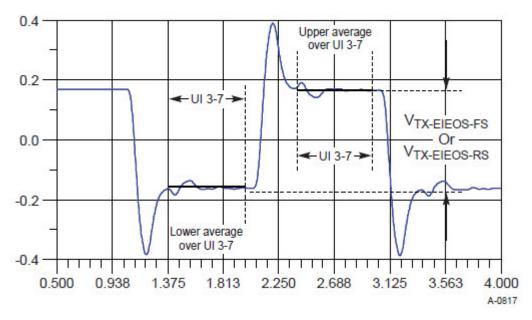

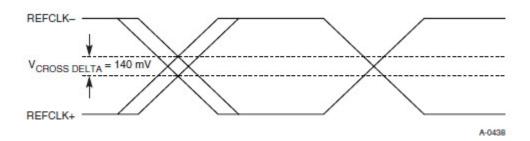

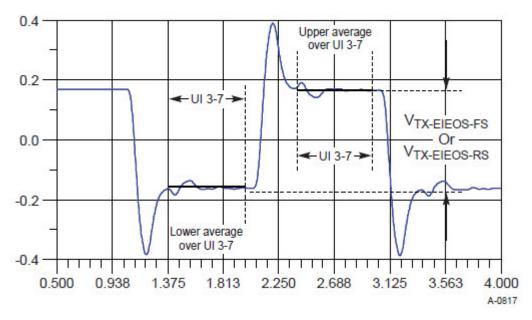

Figure 12 Single-Ended Measurement Points for Delta Cross Point

#### Understanding the Test Flow

The PCI Express test application performs the following automated steps for measuring the test results based on the above mentioned references:

- 1 Fits and displays all sample data on screen.

- 2  $\,$  Uses MATLAB function to find the variation of  $V_{\mbox{\footnotesize{CROSS}}}.$  The MATLAB function does the following:

- a Finds crossing edges for rising and falling edges.

- b Finds delta crossing for rising edge of RefClk+ and falling edge of RefClk-.

- 3 Finds the differential value between maximum crossing rising edge and minimum crossing rising edge as variation of  $V_{\text{Cross}}$ .

- 4 Reports the measurement results and verifies that the value of the parameter is as per the conformance limits specified in the PCI Express Base Specification, Rev 5.0, Section 8.6.2, Table 8-16 as variation of  $V_{\rm Cross} < 140~{\rm mV}$ .

#### Viewing Test Results

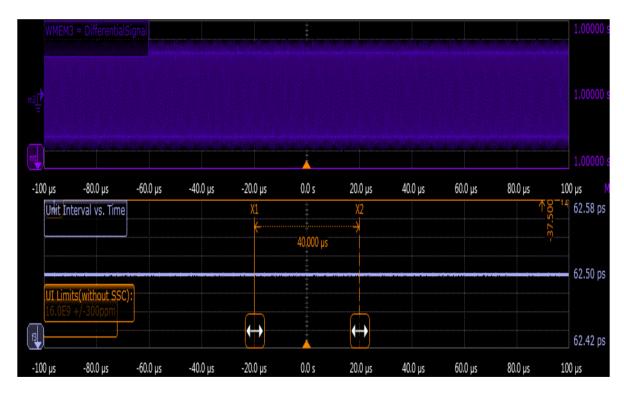

#### Clock Frequency (Common Clk)

This test verifies that the measured reference clock frequency, F<sub>REFCLK</sub>, is within than the allowed frequency range.

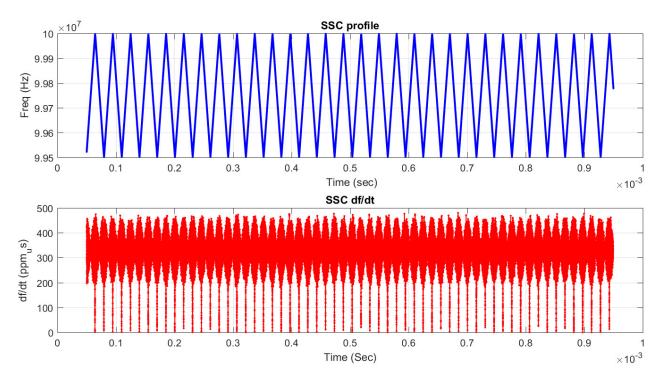

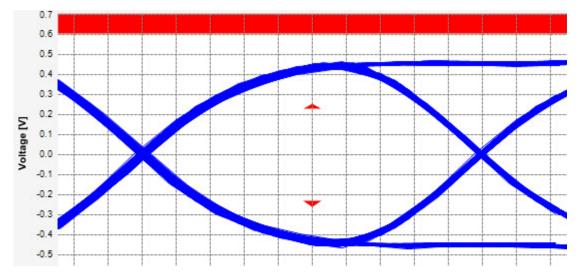

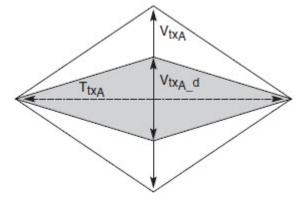

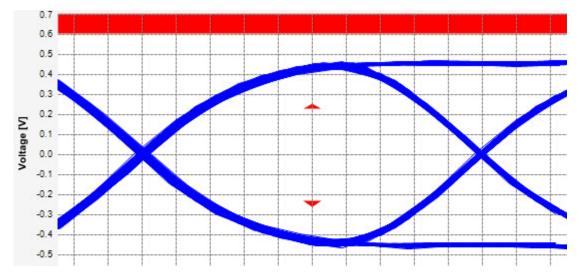

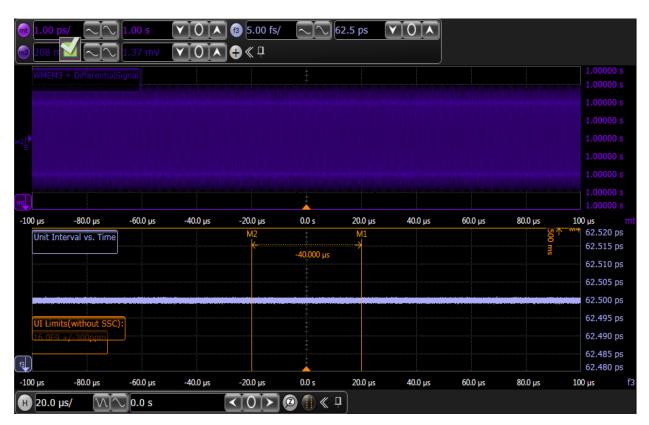

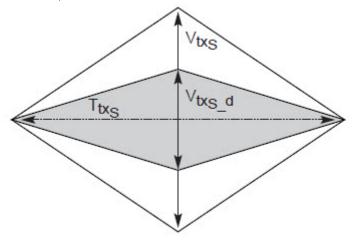

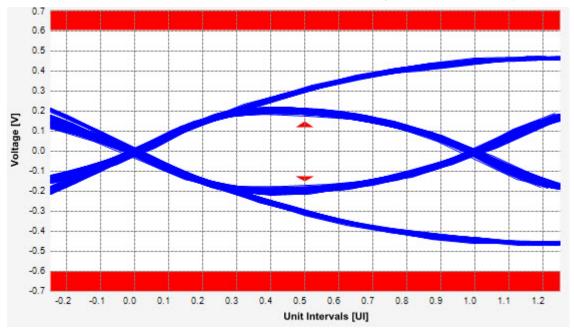

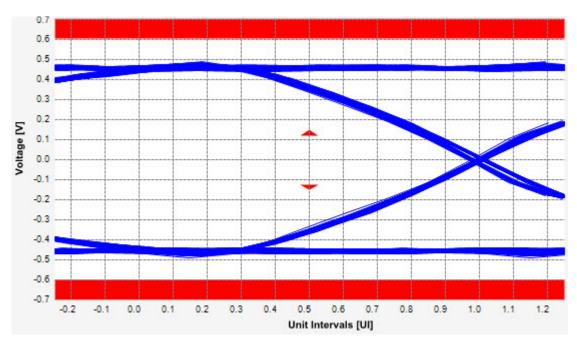

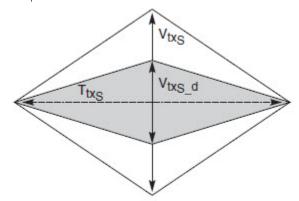

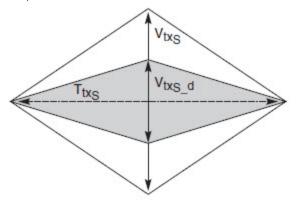

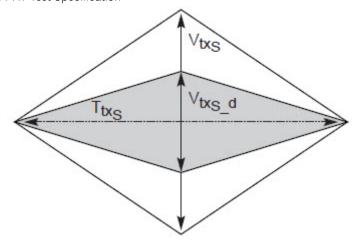

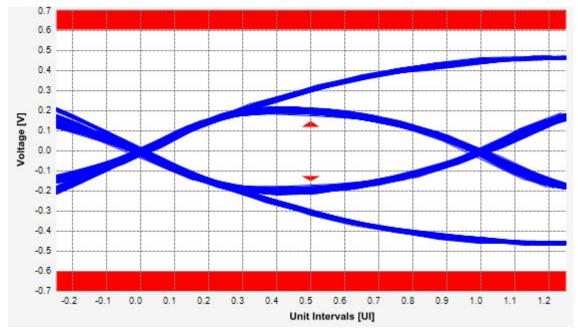

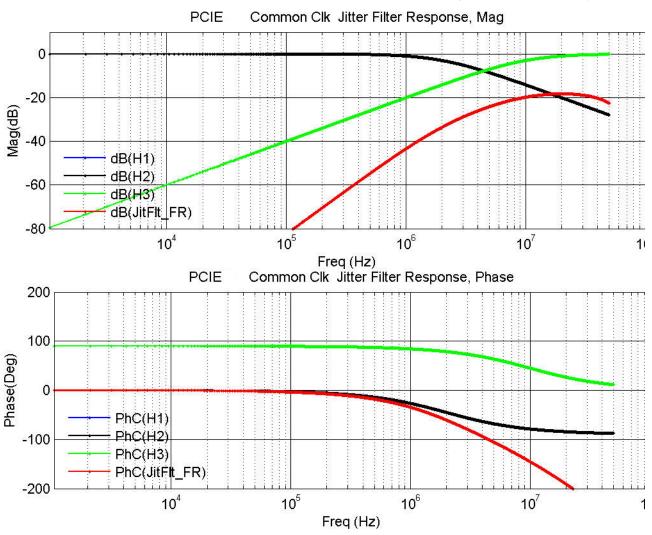

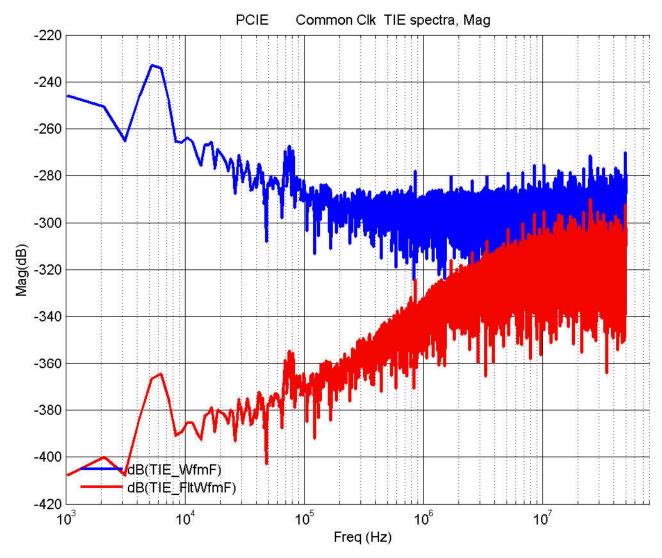

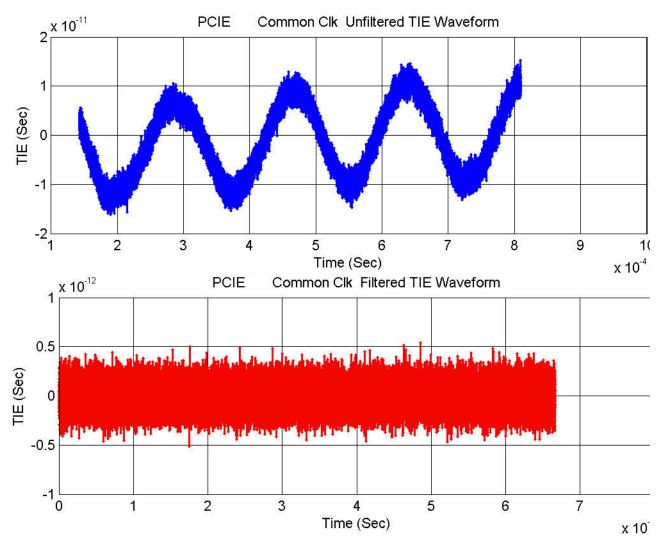

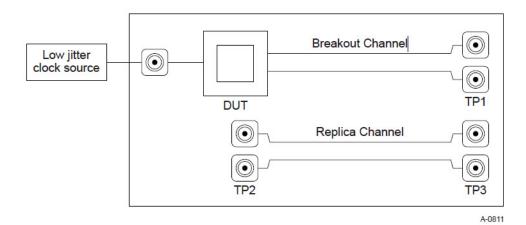

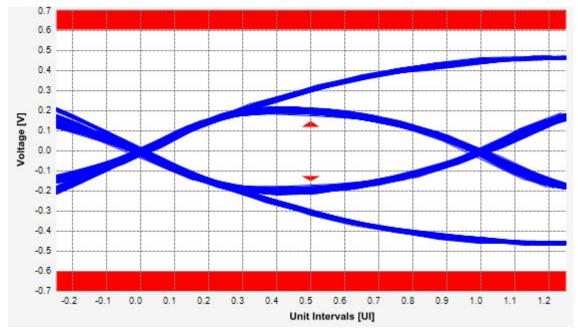

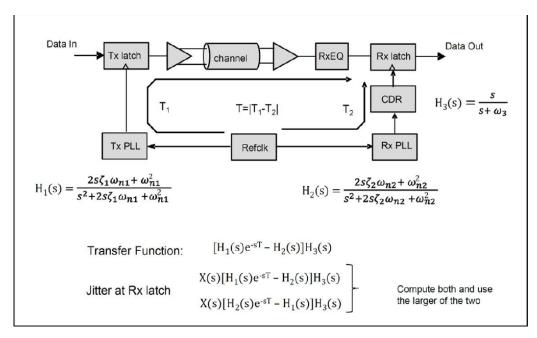

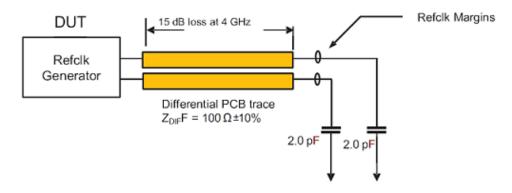

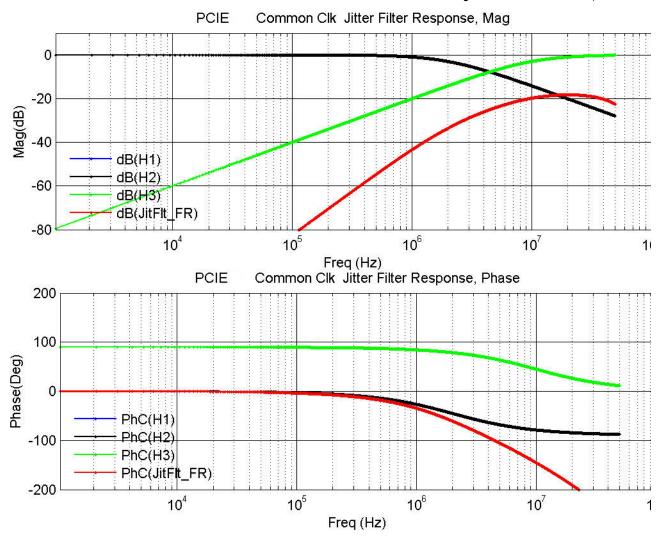

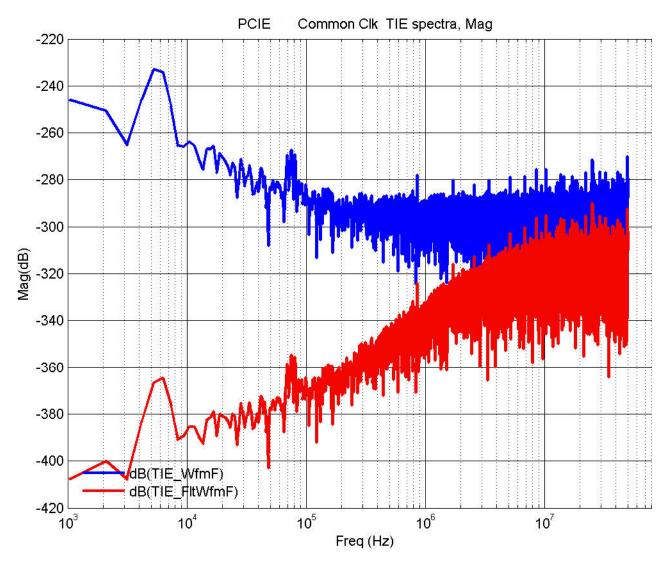

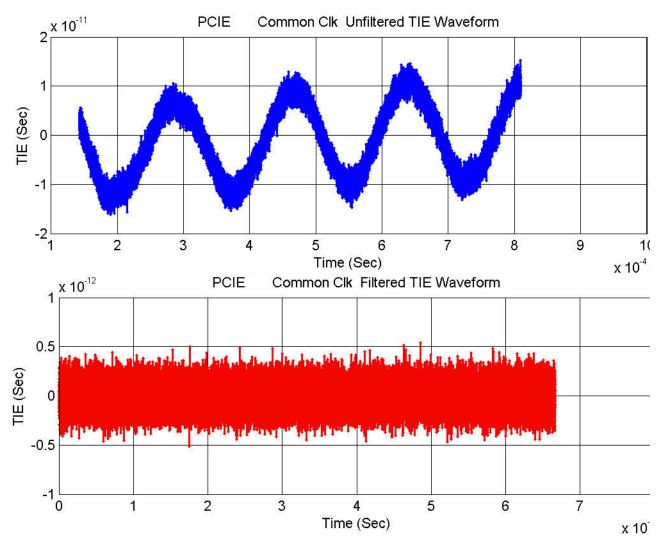

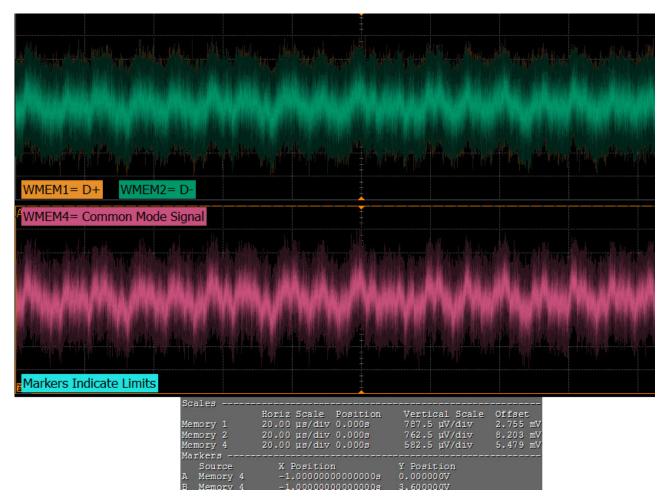

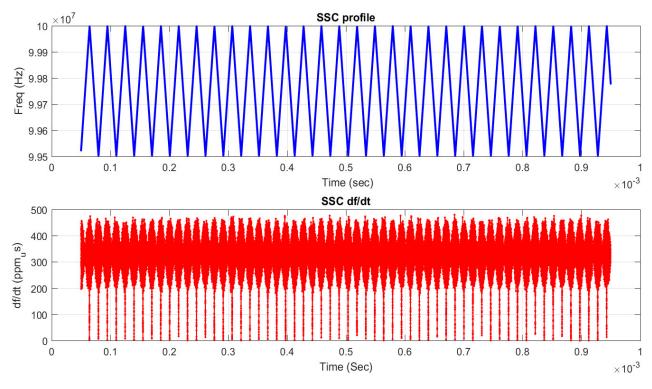

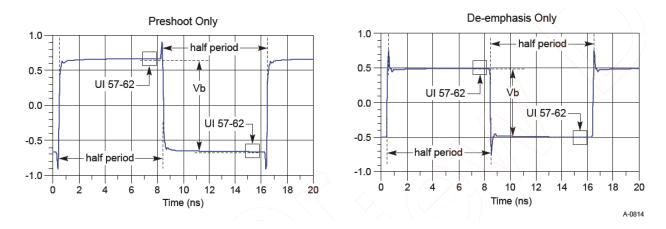

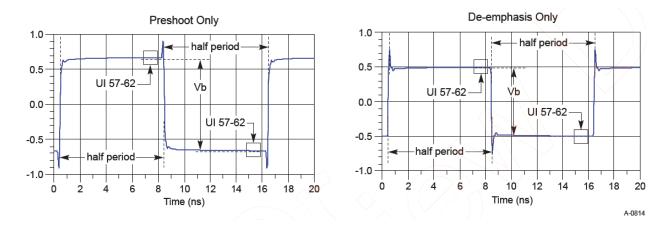

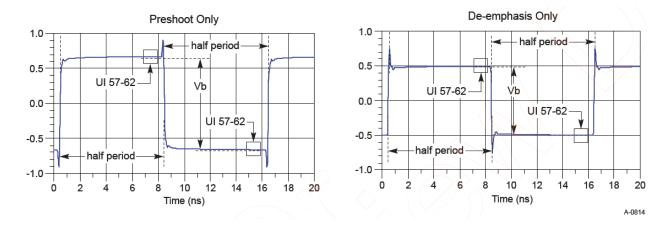

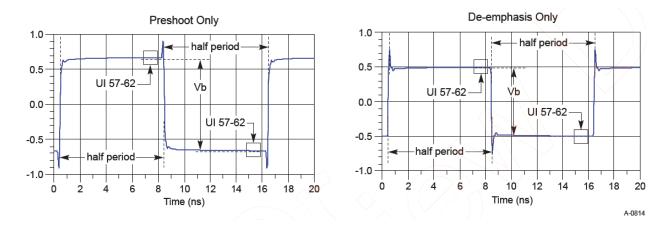

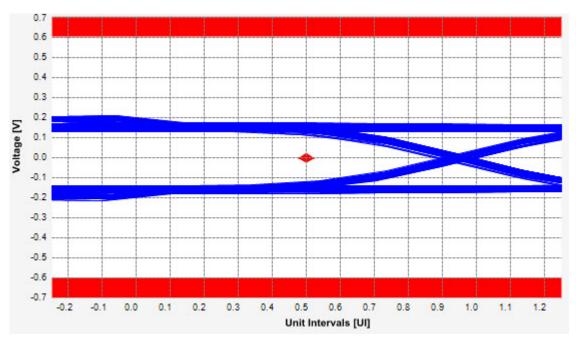

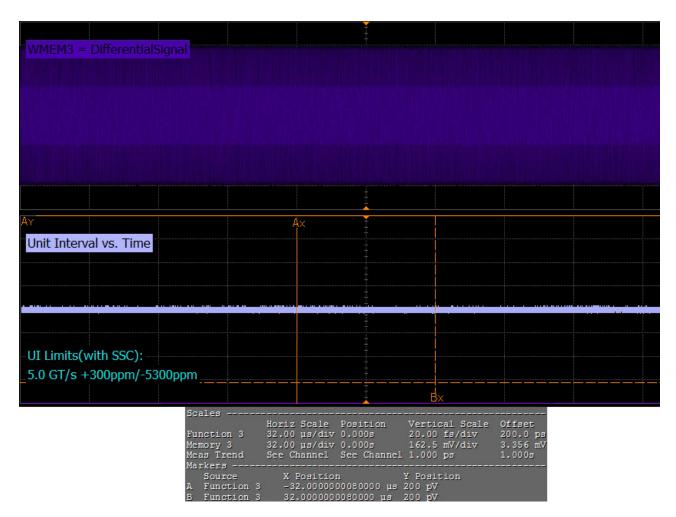

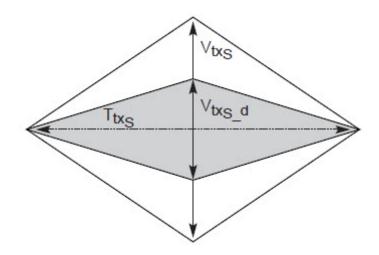

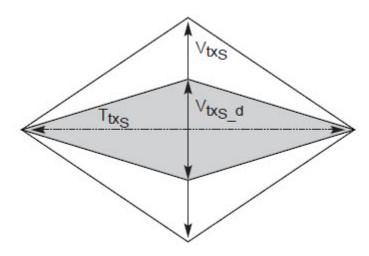

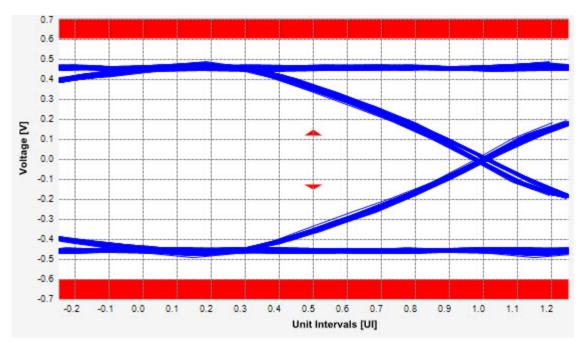

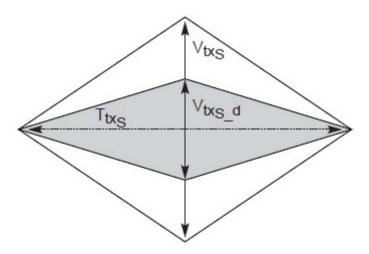

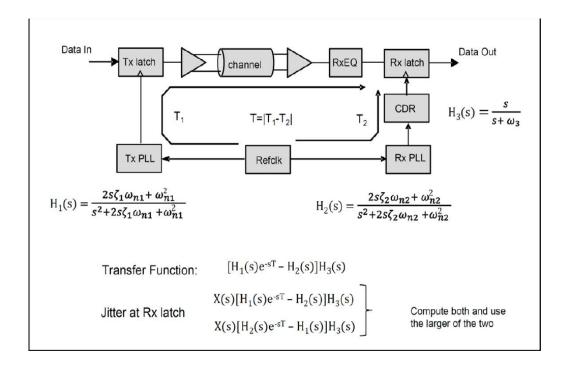

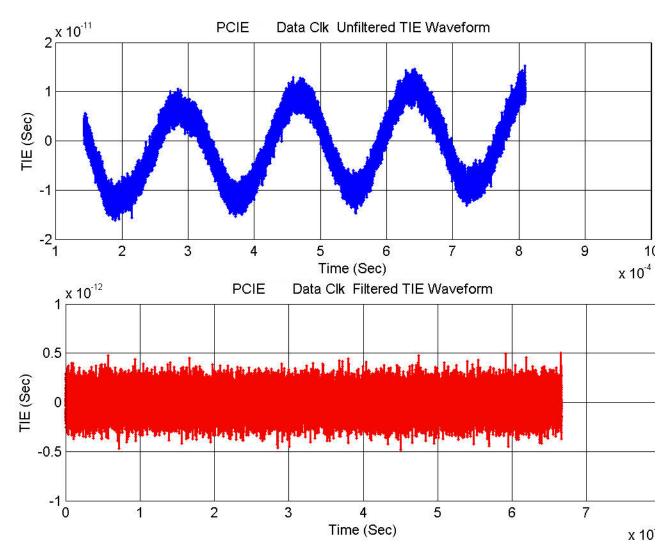

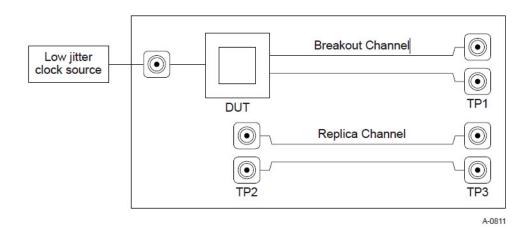

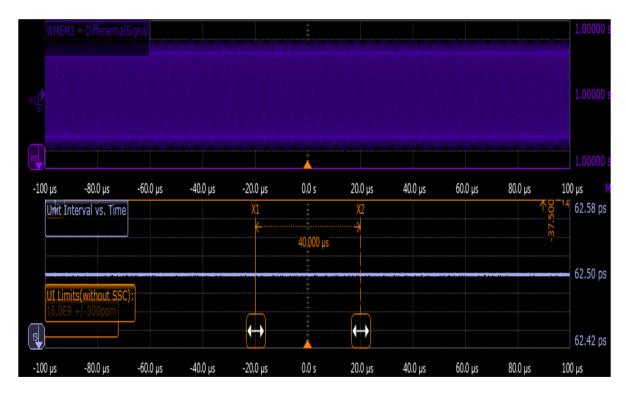

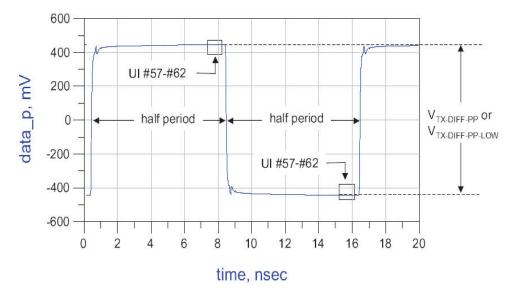

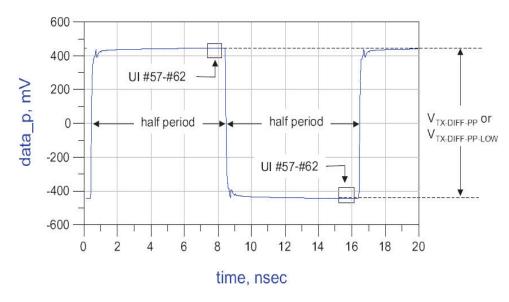

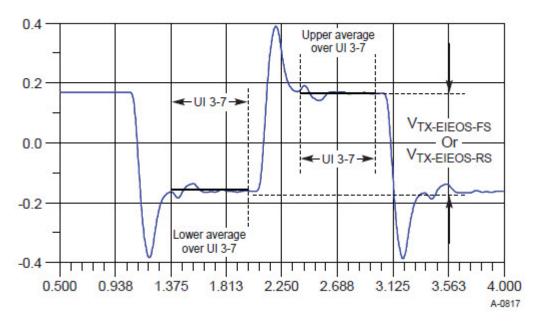

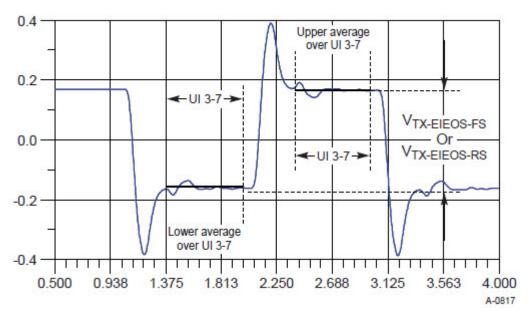

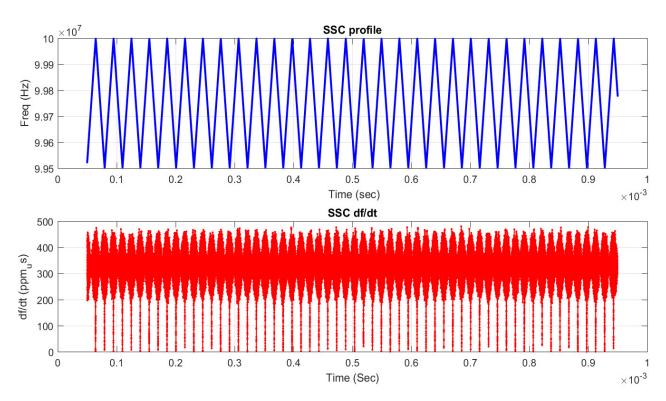

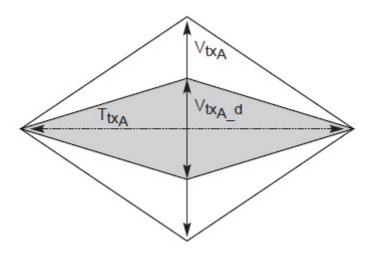

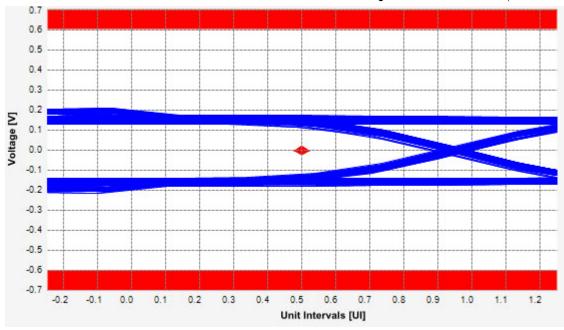

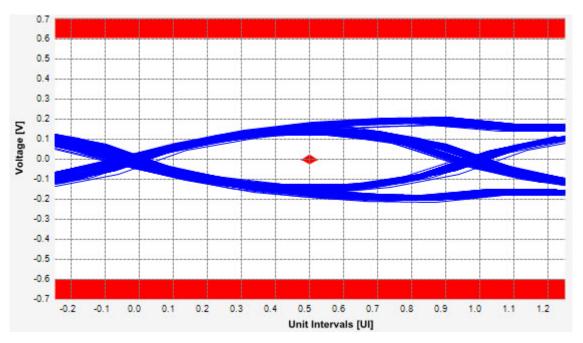

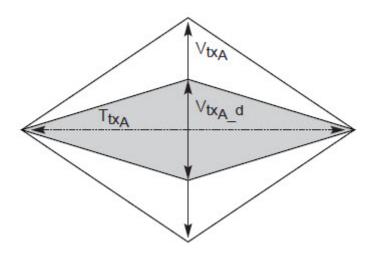

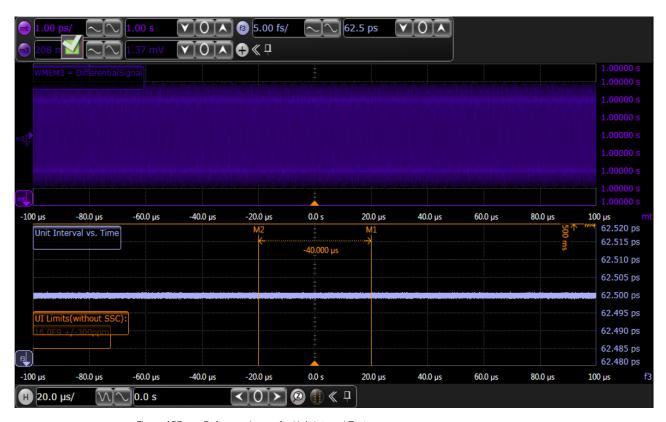

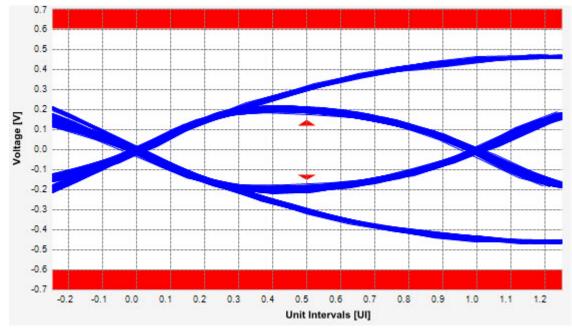

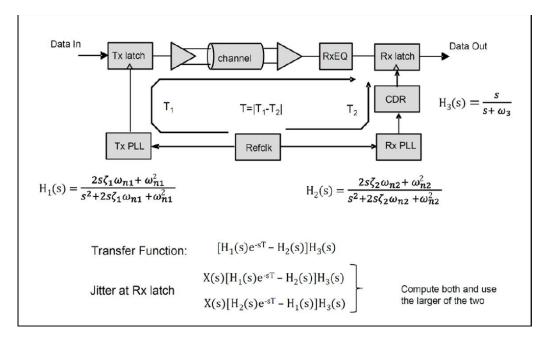

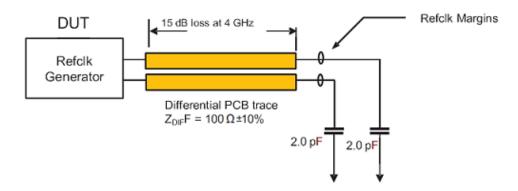

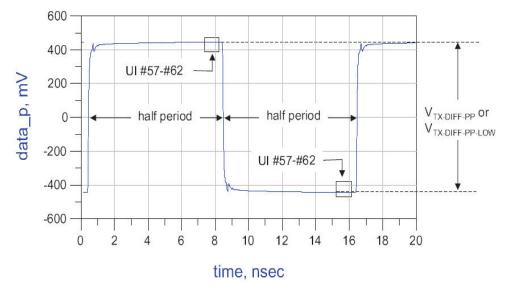

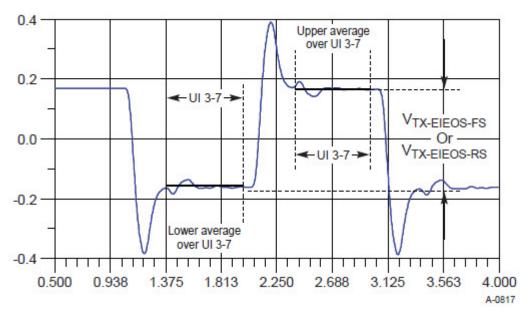

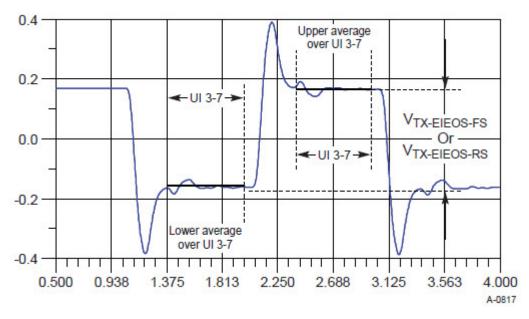

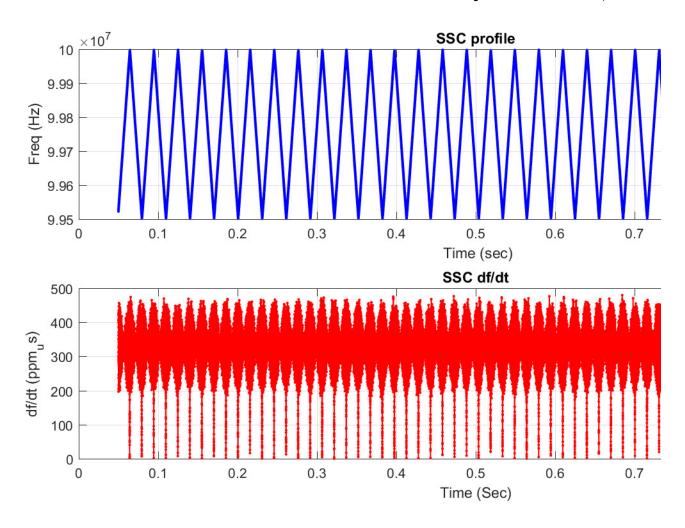

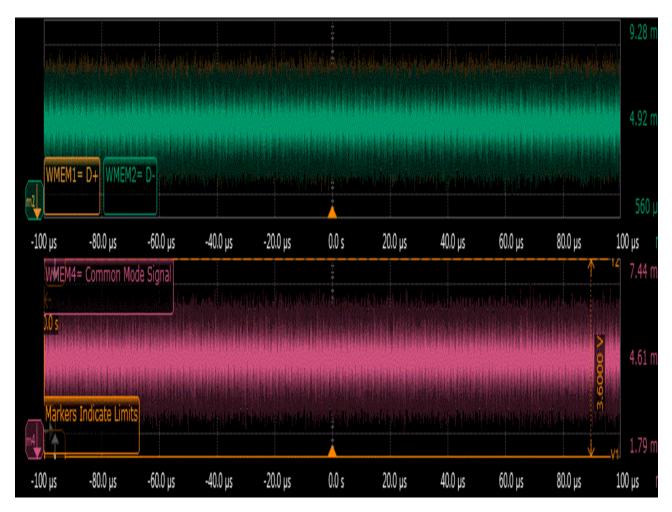

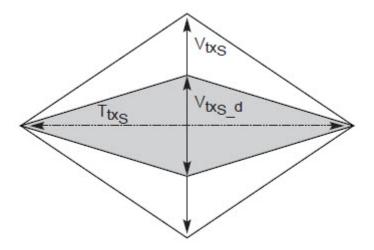

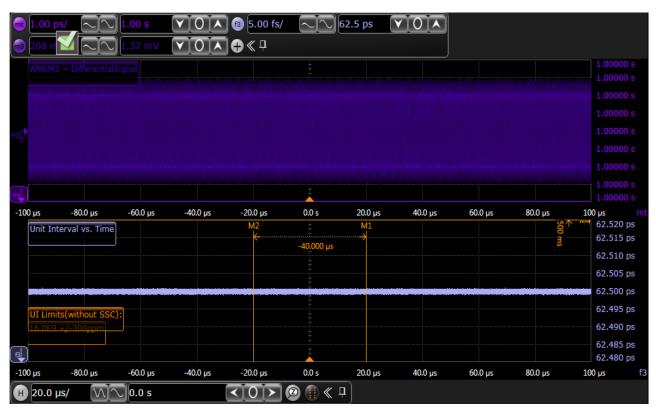

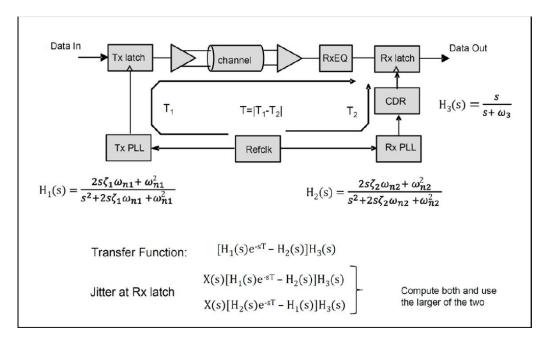

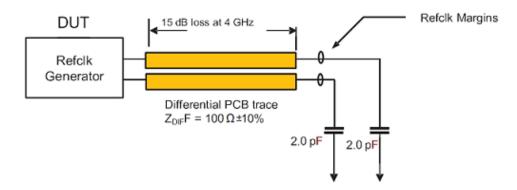

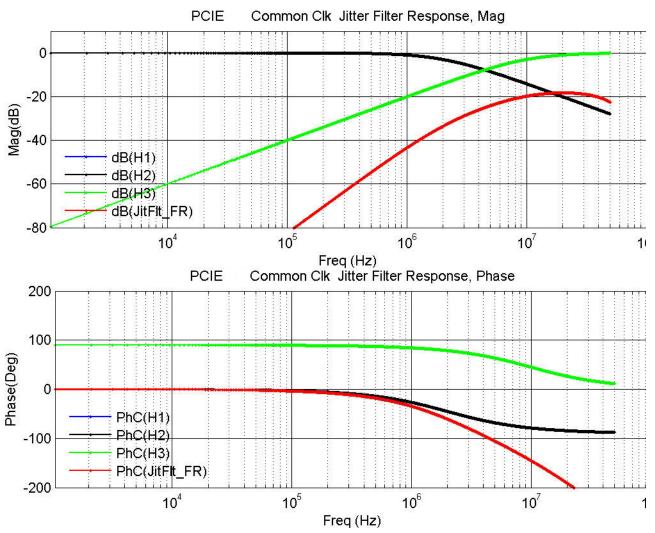

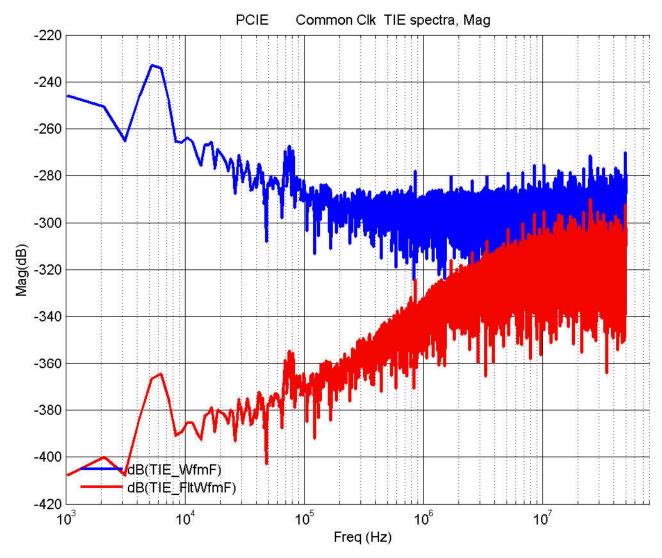

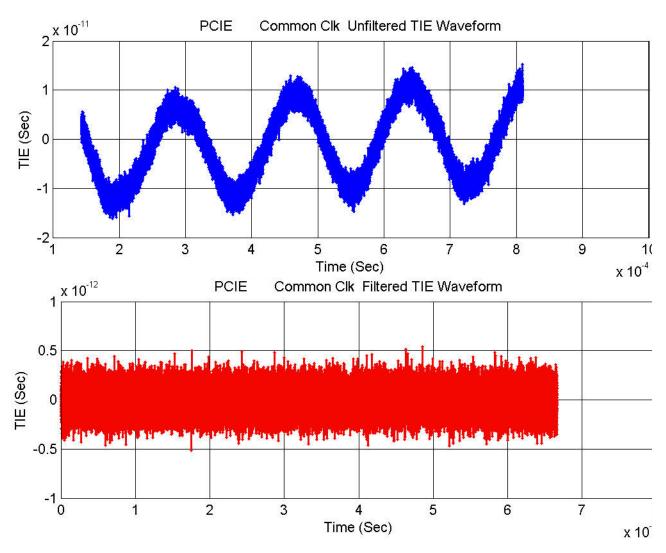

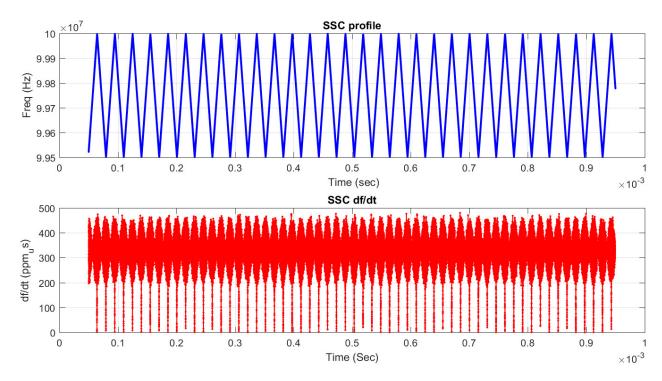

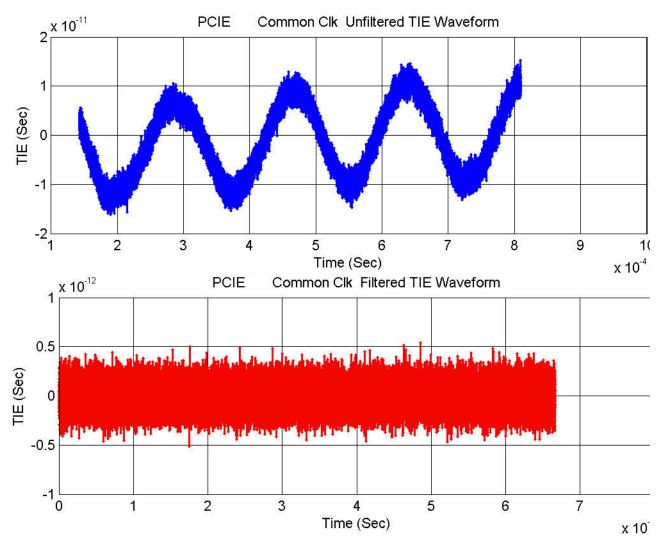

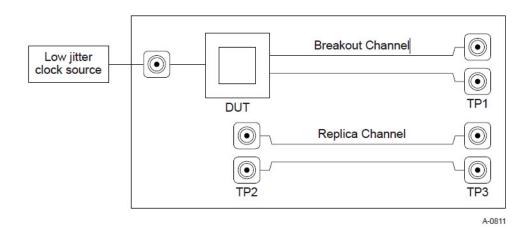

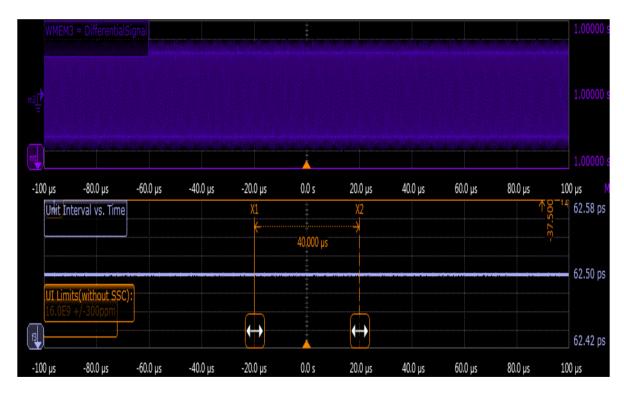

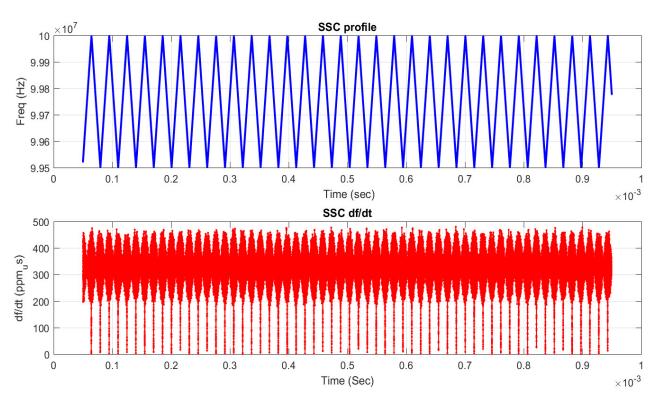

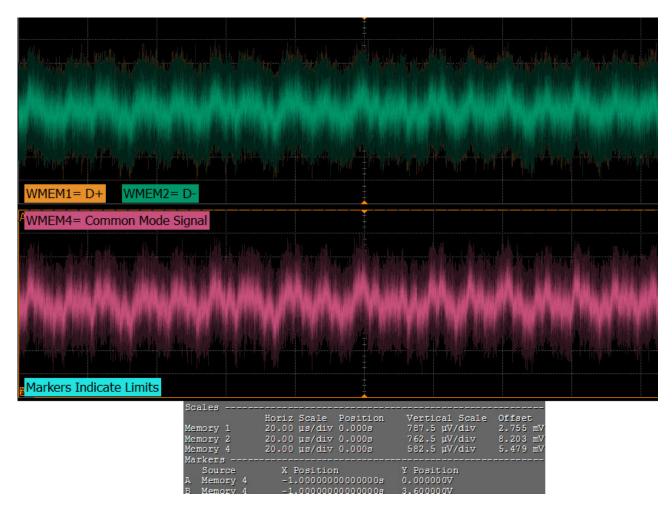

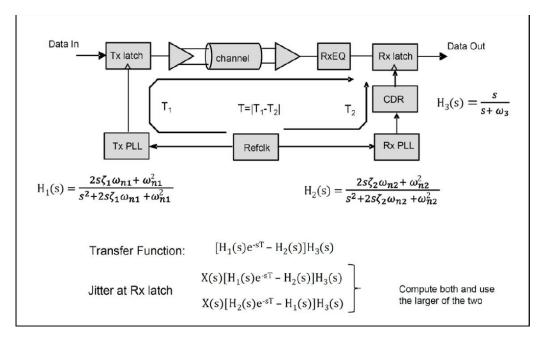

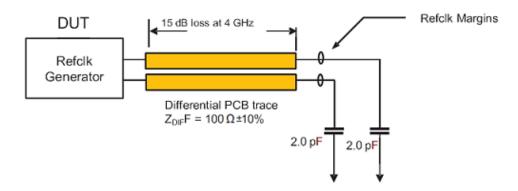

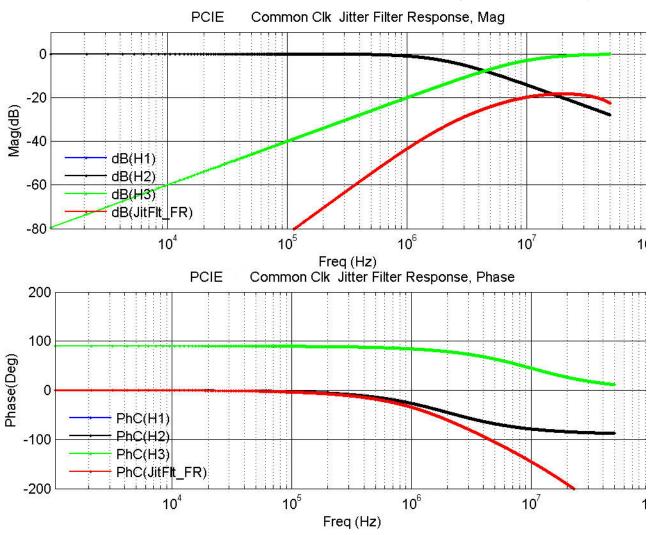

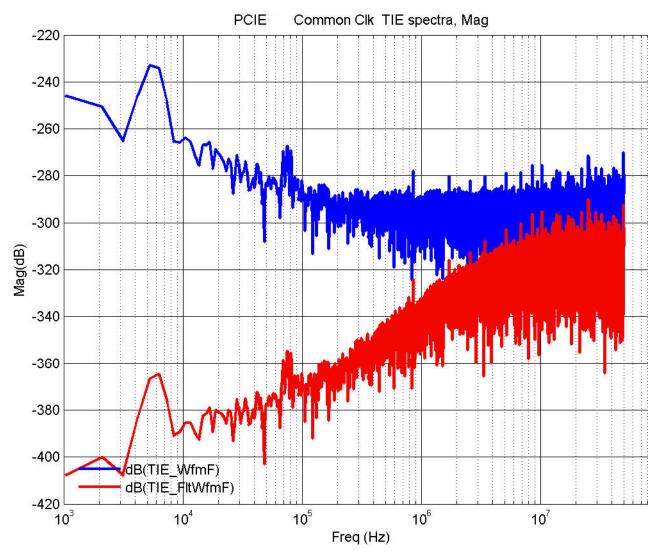

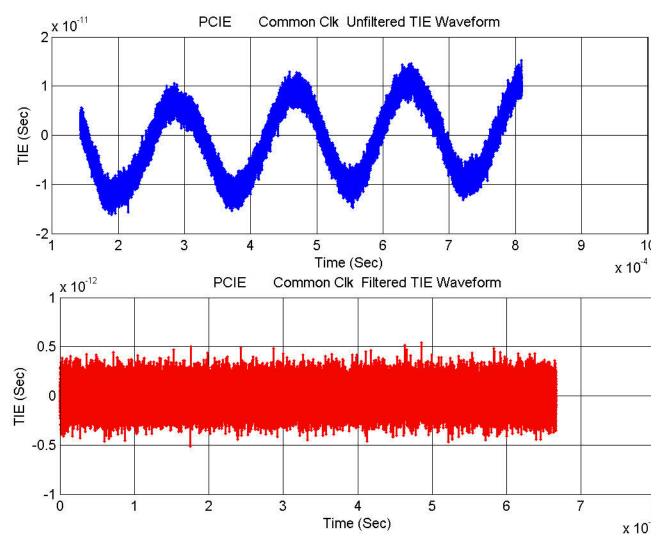

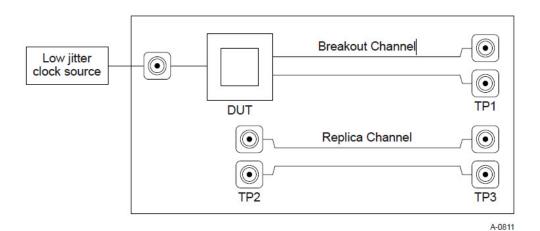

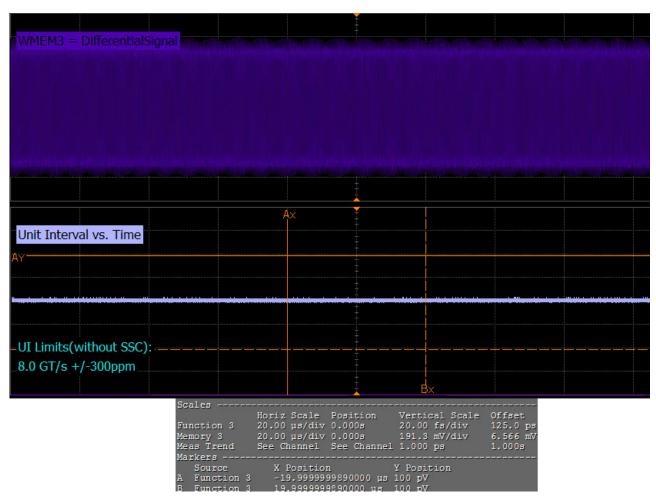

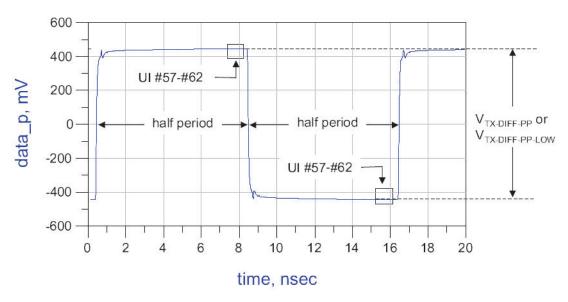

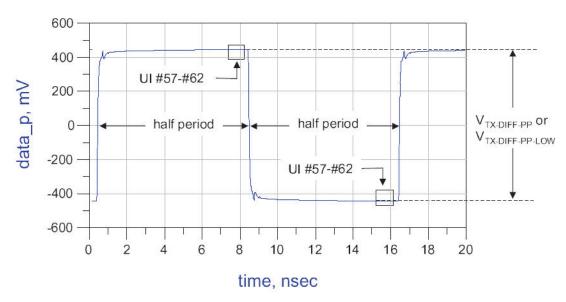

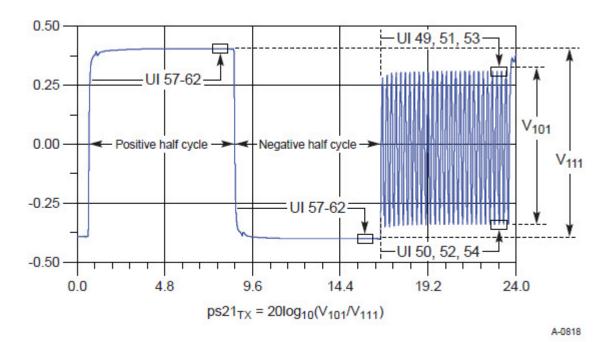

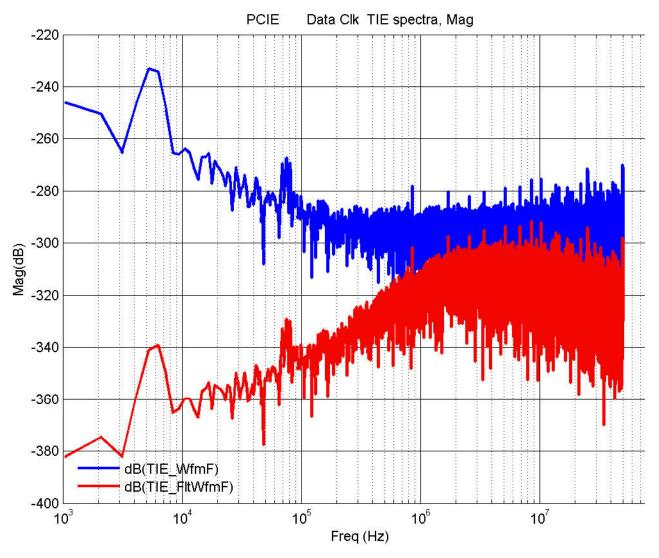

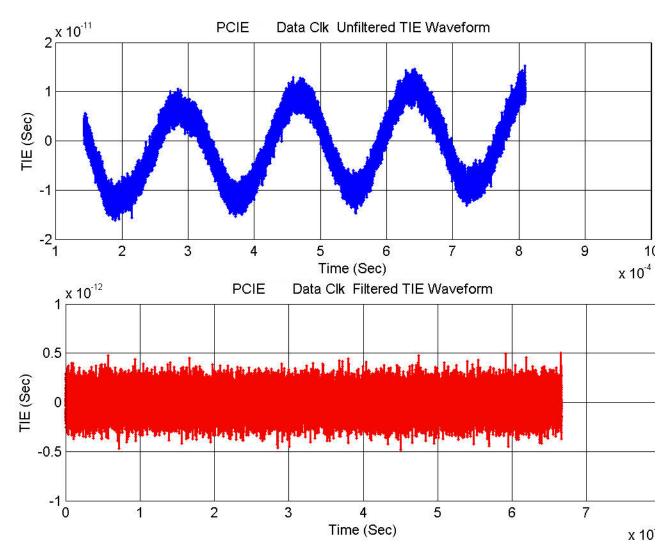

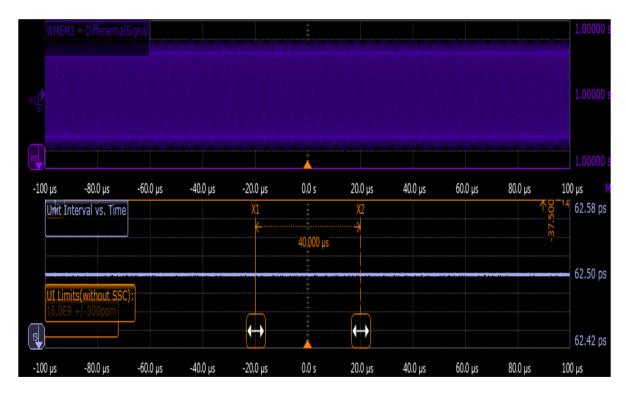

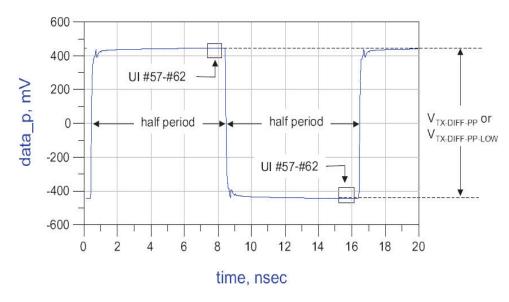

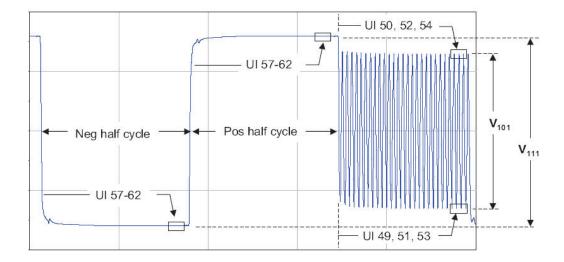

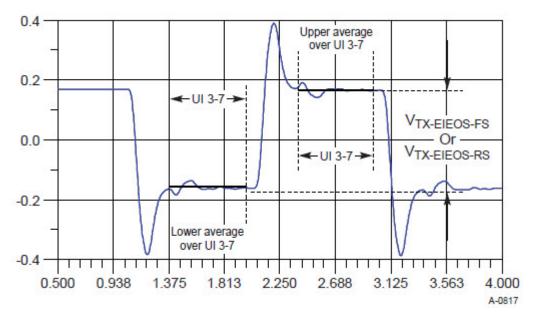

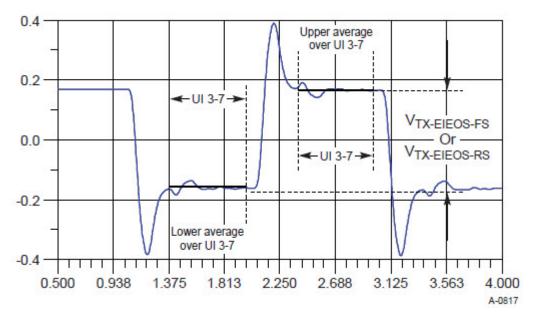

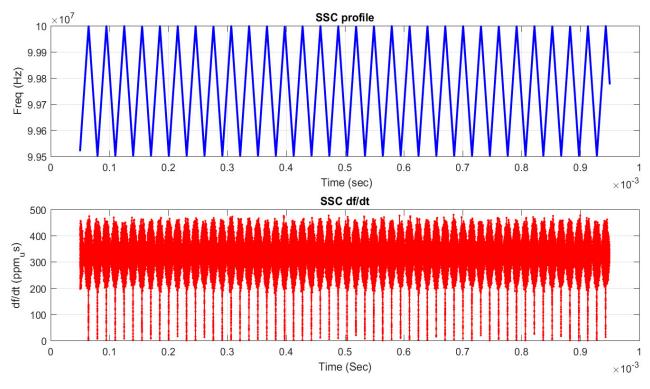

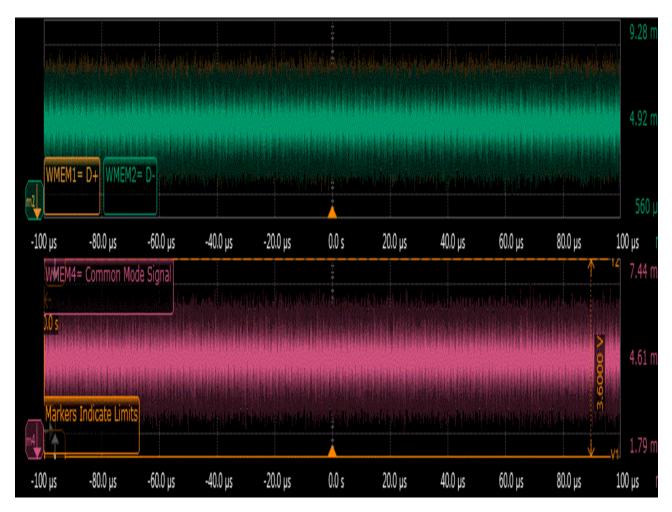

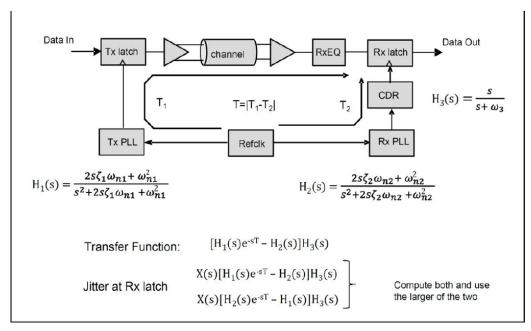

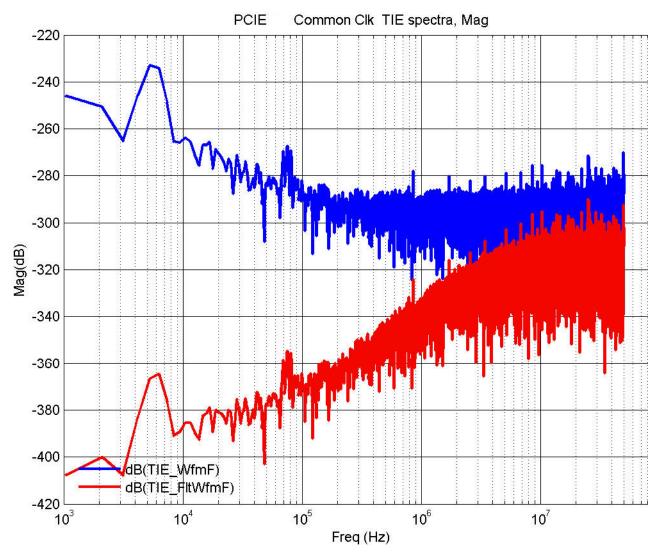

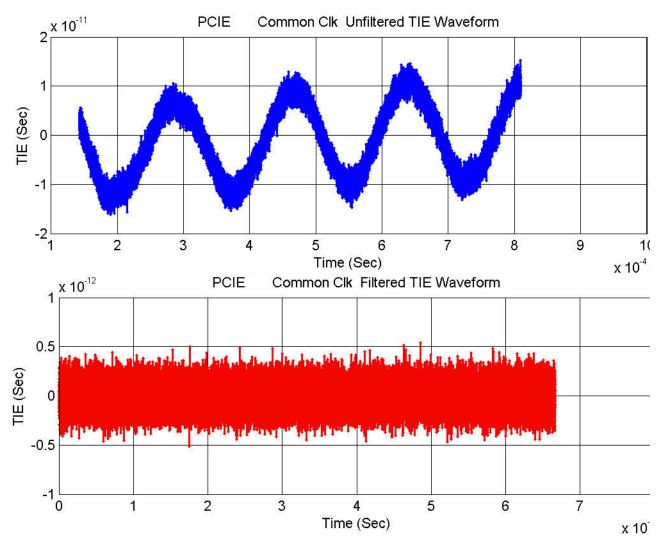

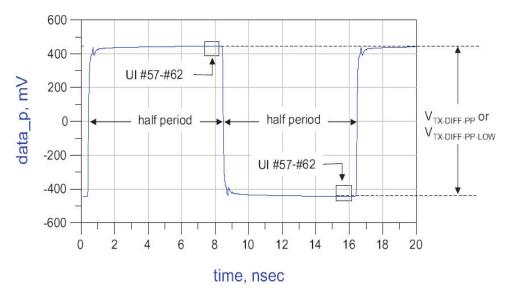

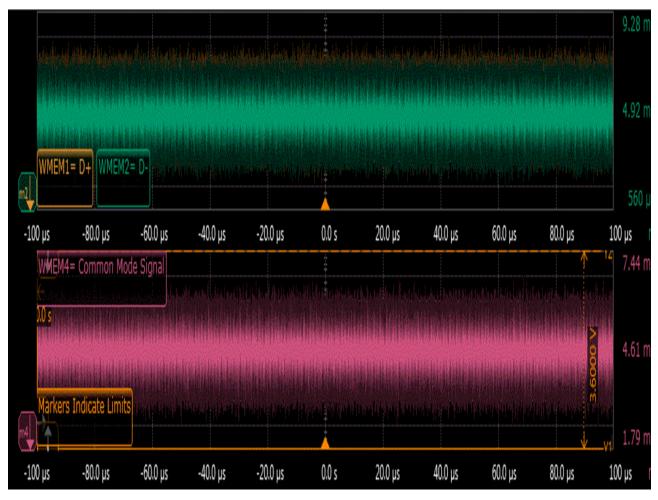

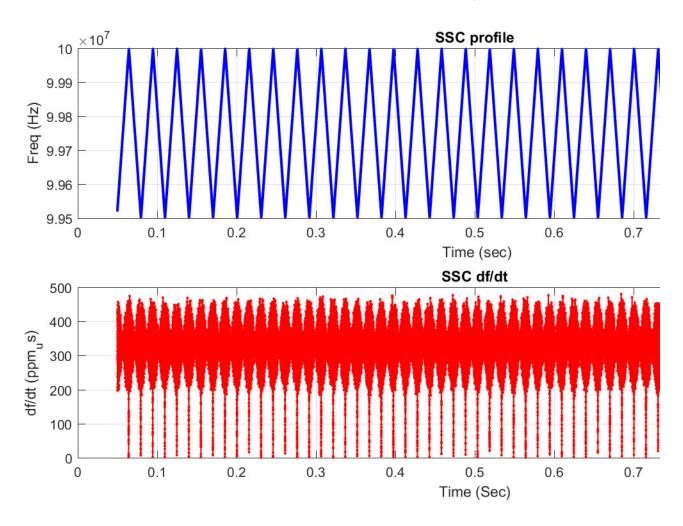

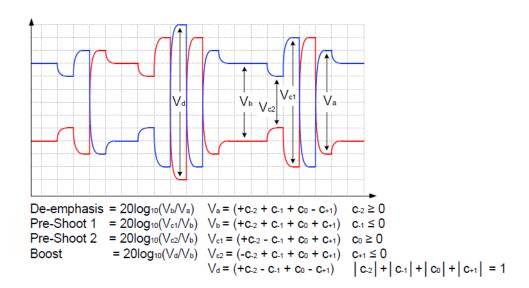

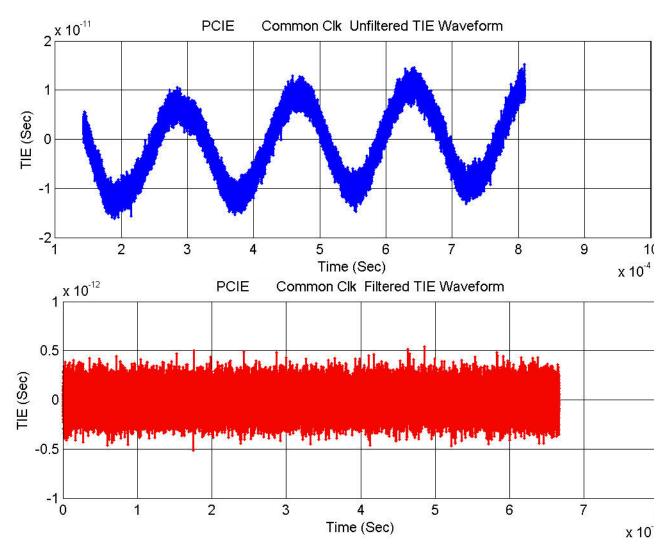

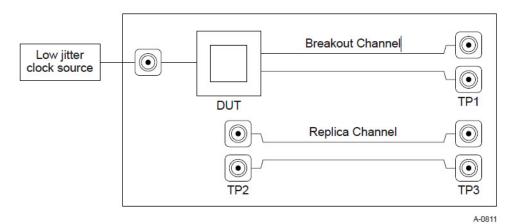

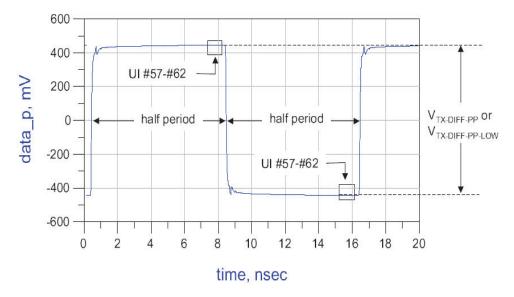

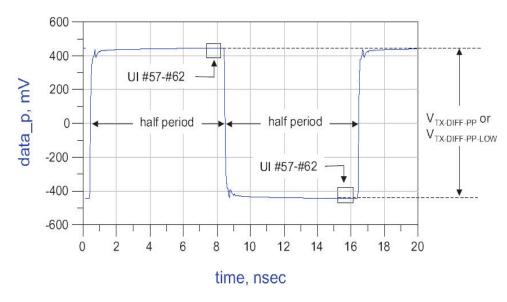

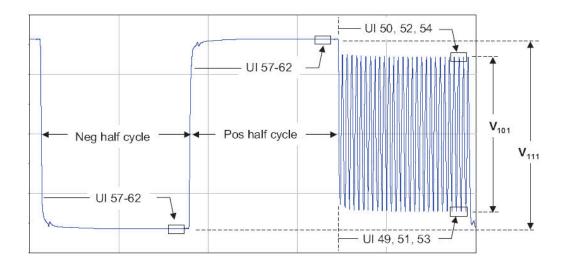

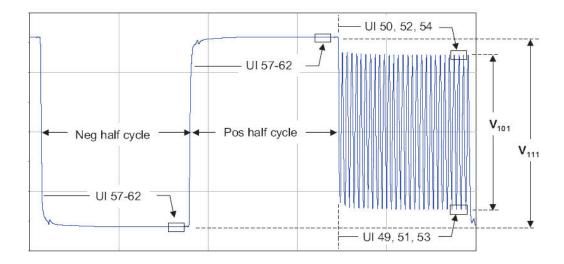

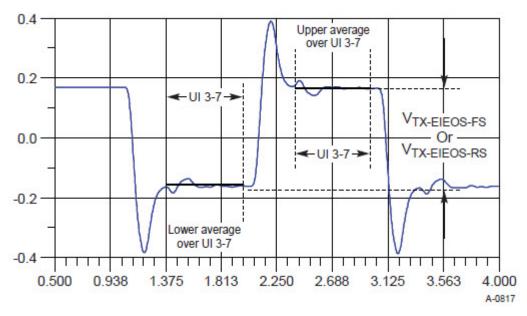

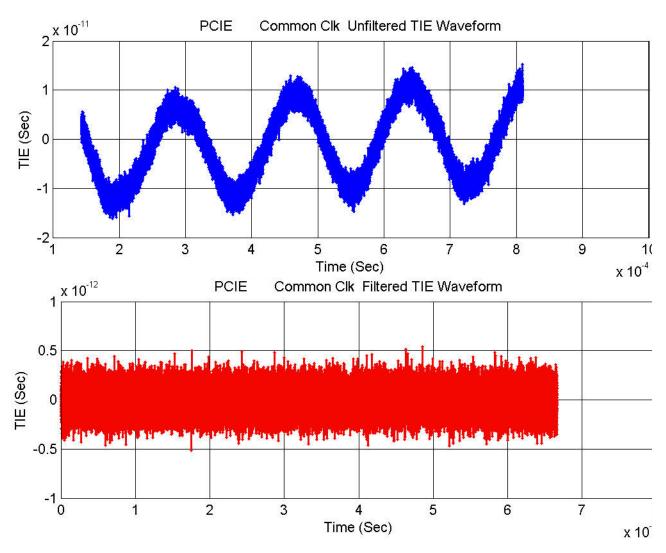

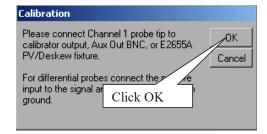

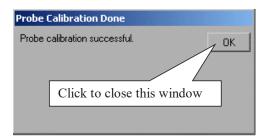

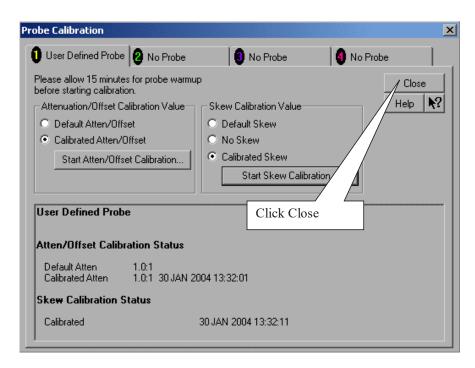

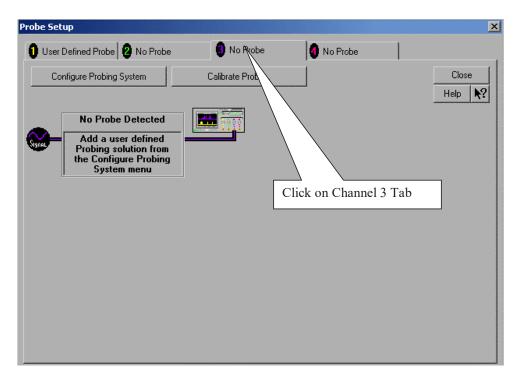

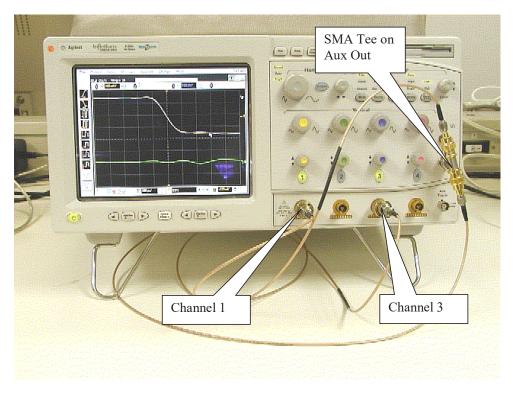

#### Test Reference